Plik Pętla synchronizacji fazowej jest jednym z podstawowych bloków w nowoczesnych systemach elektronicznych. Jest powszechnie używany w multimediach, komunikacji i wielu innych zastosowaniach. Istnieją dwa różne typy PLL - liniowe i nieliniowe. Nieliniowe są trudne i skomplikowane do zaprojektowania w rzeczywistym świecie, ale teoria sterowania liniowego jest dobrze modelowana w analogowych PLL. PLL dowiodło, że model liniowy jest wystarczający dla większości zastosowań elektronicznych.

Co to jest pętla z synchronizacją fazową?

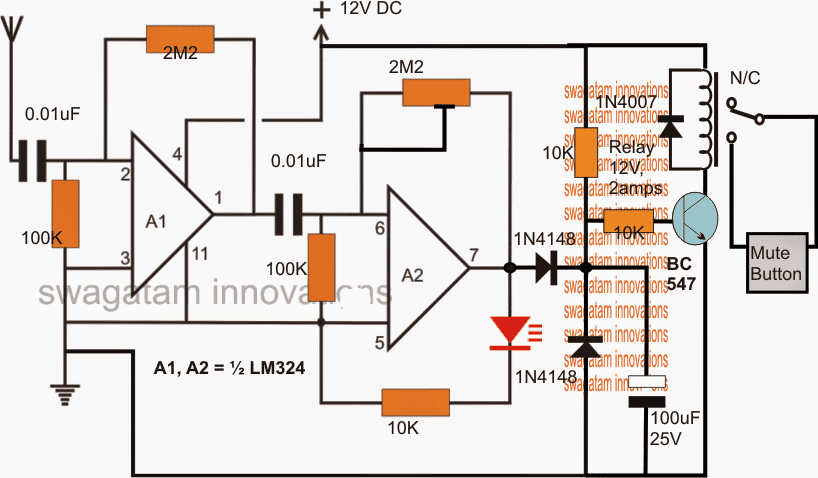

Pętla z synchronizacją fazową składa się z detektora fazy i oscylatora sterowanego napięciem. Wyjście detektora fazy jest wejściem oscylatora sterowanego napięciem (VCO), a wyjście VCO jest podłączone do jednego z wejść detektora fazy, co pokazano poniżej na podstawowym schemacie blokowym. Kiedy te dwa urządzenia są połączone, tworzy się pętla.

PODSTAWOWY SCHEMAT PĘTLI ZABLOKOWANEJ W FAZIE

Schemat blokowy i zasada działania PLL

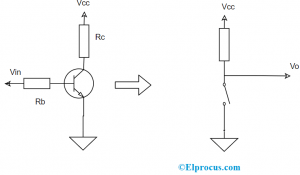

Pętla synchronizacji fazy składa się z detektora fazy, a oscylator sterowany napięciem a pomiędzy nimi zamocowany jest filtr dolnoprzepustowy. Sygnał wejściowy „Vi” o częstotliwości wejściowej „Fi” jest poddawany kontroli przez detektor fazy. Zasadniczo detektor fazy to komparator który porównuje częstotliwość wejściową fi przez częstotliwość sprzężenia zwrotnego fo. Wyjście detektora fazy to (fi + fo), które jest napięciem stałym. Poza detektorem fazy, tj. Napięcie DC jest doprowadzane do filtra dolnoprzepustowego (LPF), usuwa szum o wysokiej częstotliwości i wytwarza stały poziom DC, tj. Fi-Fo. Vf jest również dynamiczną cechą PLL.

Schemat blokowy PLL

Wyjście filtra dolnoprzepustowego, tj. Poziom DC jest przekazywany do VCO. Sygnał wejściowy jest wprost proporcjonalny do częstotliwości wyjściowej VCO (fo). Częstotliwości wejściowe i wyjściowe są porównywane i regulowane za pomocą pętli sprzężenia zwrotnego, aż częstotliwość wyjściowa będzie równa częstotliwości wejściowej. Dlatego PLL działa jak swobodny bieg, przechwytywanie i blokada fazy.

Gdy nie jest przyłożone napięcie wejściowe, mówi się, że jest to stopień swobodny. Gdy tylko częstotliwość wejściowa zastosowana do VOC zmieni się i wytworzy częstotliwość wyjściową do porównania, nazywa się to etapem przechwytywania. Poniższy rysunek przedstawia schemat blokowy PLL.

Detektor pętli fazowej

Detektor pętli synchronicznej porównuje częstotliwość wejściową i wyjściową VCO w celu wytworzenia napięcia stałego, które jest wprost proporcjonalne do rozróżnienia faz między dwiema częstotliwościami. Sygnały analogowe i cyfrowe są używane w pętli synchronizacji fazy. Większość monolitycznych PLL obwody scalone używaj analogowego detektora fazy, a większość detektorów fazy jest typu cyfrowego. Obwód podwójnie zbalansowanej mieszanki jest powszechnie stosowany w detektorach fazy analogowej. Poniżej przedstawiono niektóre popularne detektory fazy:

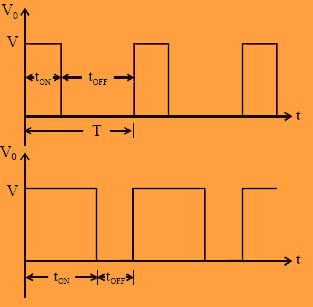

Ekskluzywny detektor fazy OR

Ekskluzywny detektor fazy OR to CMOS IC 4070. Częstotliwości wejściowe i wyjściowe są stosowane do detektora fazy EX OR. Aby uzyskać wysoki poziom wyjściowy, przynajmniej jedno wejście powinno być niskie, a inne warunki wyjściowe są niskie, co pokazano w poniższej tabeli prawdy. Rozważmy przebieg, częstotliwości wejściowe i wyjściowe, czyli fi i fo mają różnicę faz równą 0 stopni. Wówczas napięcie wyjściowe DC komparatora będzie funkcją różnicy faz między dwoma wejściami.

| być | fo | Vdc |

Niska | Niska | Niska |

Niska | wysoki | wysoki |

wysoki | Niska | wysoki |

Wysoki | Wysoki | Niska |

Funkcje różnicy faz między fi i fo przedstawiono na wykresie napięcia wyjściowego DC. Jeśli detektor fazy ma 180 stopni, napięcie wyjściowe jest maksymalne. Jeśli zarówno częstotliwość wejściowa, jak i wyjściowa są falami prostokątnymi, stosuje się ten typ detektorów fazy.

Ekskluzywny detektor fazy OR

Detektor fazy wyzwalania krawędzi

Detektor fazy wyzwalania zboczem jest używany, gdy częstotliwości wejściowe i wyjściowe mają kształt fali impulsu, który jest mniejszy niż 50% cyklu pracy. Przerzutnik R-S jest używany do detektorów fazy, co pokazano na poniższym rysunku. Do od R-S flip flop , dwie bramki NOR są sprzężone krzyżowo. Wyjście detektora fazy może zmienić swój stan logiczny poprzez wyzwolenie przerzutnika R-S. Dodatnie zbocze częstotliwości wejściowej i wyjściowej może zmienić sygnał wyjściowy detektora fazy.

Detektor fazy wyzwalania krawędzi

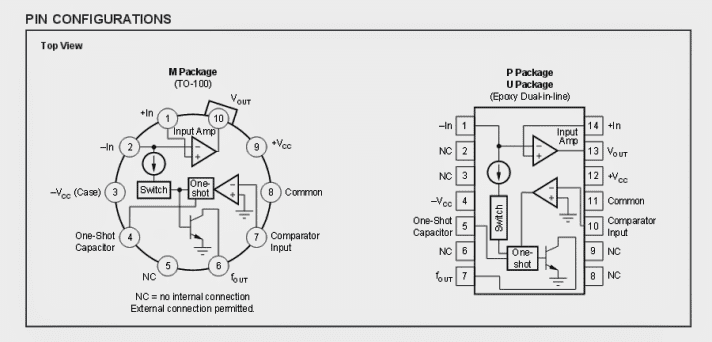

Monolityczny detektor fazy

Monolityczny detektor fazy jest typu CMOS, tj. IC 4044. Jest on silnie kompensowany czułością na harmoniczne, a problemy z cyklem pracy są porzucone, ponieważ obwód może reagować tylko na przejście sygnału wejściowego. W krytycznych zastosowaniach jest to najbardziej gorączkowy detektor fazy. Niezależne zmiany amplitudy są wolne od błędu fazy, błędu wyjściowego napięcia i współczynnika wypełnienia przebiegów wejściowych.

Zastosowania pętli fazowej

- Sieci demodulacyjne FM do operacji FM

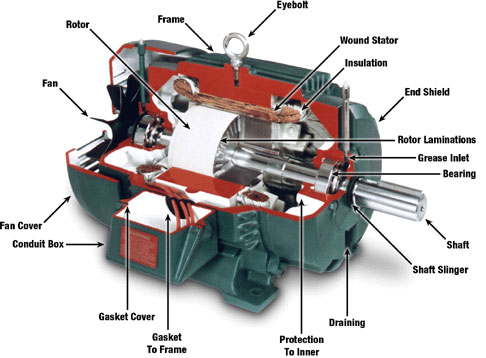

- Jest używany w sterowanie prędkością silnika i filtry śledzące.

- Jest używany w dekodowaniu z przesunięciem częstotliwości dla częstotliwości nośnych demodulacji.

- Jest używany z czasem do przetworników cyfrowych.

- Służy do redukcji jittera, tłumienia pochylenia, odzyskiwania zegara.

Chodzi o zasadę działania i działania pętli synchronizacji fazowej oraz jej zastosowania. Mamy nadzieję, że informacje zawarte w artykule pomogą Ci dowiedzieć się czegoś o projekcie i go zrozumieć. Ponadto, jeśli masz jakieś pytania dotyczące tego artykułu i na projekty elektryczne i elektroniczne możesz skomentować w poniższej sekcji. Oto pytanie do Ciebie, jaki jest najlepszy sposób symulacji PLL dla stabilności?

Kredyty fotograficzne:

- Schemat blokowy PLL obwód dziś

- Ekskluzywny detektor fazy OR sanfoundry

- Detektor fazy wyzwalania krawędzi LEARNABOUT-ELECTRONICS