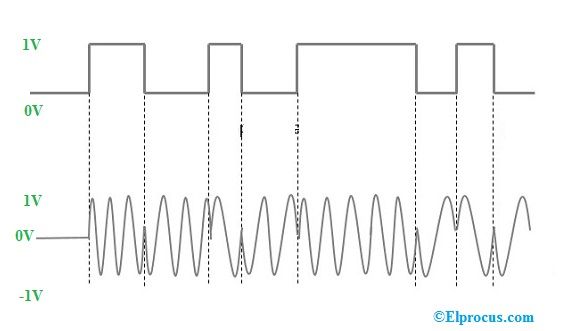

W Elektronika cyfrowa , zatrzask to jeden rodzaj obwód logiczny , i jest również znany jako bistabilny-multiwibrator . Ponieważ ma dwa stabilne stany, a mianowicie aktywny wysoki i aktywny niski. Działa jak urządzenie magazynujące, przechowując dane przez tor sprzężenia zwrotnego. Przechowuje 1-bitowe dane tak długo, jak długo urządzenie jest aktywowane. Po zadeklarowaniu włączenia natychmiast zatrzask może zmienić zapisane dane. Stale testuje wejścia po aktywacji sygnału zezwolenia. Praca tych obwodów może odbywać się w 2 stanach w oparciu o wysoki lub niski sygnał zezwolenia. Gdy obwód zatrzasku jest w aktywnym stanie wysokim, oba i / ps są niskie. Podobnie, gdy obwód zatrzasku jest wtedy w aktywnym stanie niskim, oba i / ps są wysokie.

Różne rodzaje zamków

Zatrzaski można podzielić na różne typy, w tym zatrzask SR, Zamknięty zatrzask S-R , Zatrzask D. , Gated D Latch, JK Latch i T Latch.

SR Latch

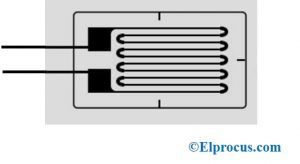

Na Zatrzask SR (ustawianie / resetowanie) jest aparatem asynchronicznym i pracuje oddzielnie dla sygnałów sterujących w zależności od stanu S i R-wejść. Poniżej przedstawiono zatrzask SR wykorzystujący bramki 2-NOR z połączeniem krzyżowym. Te zatrzaski można zbudować z Bramy NAND jednak również oba wejścia są wymieniane, a także anulowane. Nazywa się to więc zatrzaskiem SR.

SR Latch

Ilekroć linia S zatrzasku ma wysoki sygnał wejściowy, wyjście Q przechodzi w stan wysoki. W procesie sprzężenia zwrotnego wyjście Q pozostanie wysokie, gdy wejście S ponownie spadnie do stanu niskiego. W ten sposób zatrzask działa jako urządzenie pamięci.

Podobnie, wysoki sygnał wejściowy jest podawany do linii R zatrzasku, a następnie wyjście Q przechodzi w stan niski (i Q ’wysoki), a następnie pamięć zatrzasku zostanie skutecznie zresetowana. Gdy oba wejścia zatrzasku są w stanie niskim, pozostaje on we wcześniejszym stanie ustawionym lub resetowanym. Plik tabela przejść stanów lub tabela prawdy zatrzasku SR pokazano poniżej.

| S | R | Q | Q ” |

| 0 | 0 | Zatrzask | Zatrzask |

0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

1 | 1 | 0 | 0 |

Gdy oba sygnały wejściowe są jednocześnie wysokie, pojawia się problem: mówi się, że ma jednocześnie generować wysokie Q i niskie Q. To generuje stan wyścigu w obwodzie albo przerzutnik osiągnie coś w zmianie jako pierwszy, zareaguje na drugi i ogłosi się . Najlepiej jedno i drugie Bramki logiczne są równe i urządzenie będzie znajdować się w niezdefiniowanym stanie przez czas nieokreślony.

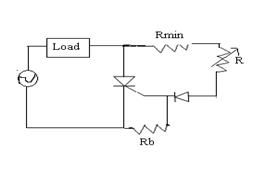

Bramowany zatrzask SR

W niektórych przypadkach popularne może być zamawianie, gdy zatrzask może i nie może się zatrzasnąć. Proste rozszerzenie pliku Zatrzask SR to nic innego jak zamykany zatrzask SR . Daje linię Enable, która powinna być ustawiona wysoko, zanim informacje będą mogły zostać zatrzaśnięte. Chociaż linia sterująca jest konieczna, zatrzask nie jest synchroniczny ze względu na wejścia, które mogą zmieniać wyjście nawet w środku impulsu włączającego.

Bramowany zatrzask SR

Gdy wejście Enable jest niskie, o / ps z bramek również musi być mniejsze, dlatego wyjścia Q & Q pozostają zablokowane w kierunku wcześniejszych informacji. Po prostu, gdy włącznik i / p jest wysoki, może zmienić położenie zatrzasku, jak pokazano w formie tabelarycznej. Jak podano w linii włączania, bramkowany zatrzask SR jest równy w procesie w kierunku zatrzasku SR. Czasami linia włączania jest sygnałem CLK, jednak jest to stroboskop odczytu / zapisu.

CLK | S | R | Q (t + 1) |

0 | X | X | Q (t) (bez zmian) |

| 1 | 0 | 0 | Q (t) (bez zmian) |

1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

1 | 1 | 1 | X |

D Zatrzask

Zatrzask danych jest łatwym rozszerzeniem do bramkowanego zatrzasku SR, który eliminuje możliwość wystąpienia niedopuszczalnych stanów wejściowych. Ponieważ bramkowany zatrzask SR pozwala nam zamocować wyjście bez użycia wejść S lub R, możemy wyeliminować jedno z i / ps, napędzając oba wejścia przeciwległym sterownikiem. Eliminujemy jedno wejście i automatycznie ustawiamy je jako przeciwne do wejścia resztkowego.

D Zatrzask

Zatrzask D wyprowadza wejście D, gdy linia Enable jest w stanie wysokim, w przeciwnym razie wyjście jest takie samo, jak wejście D, gdy wejście Enable było ostatnio wysokie. Z tego powodu jest znany jako przezroczysty zatrzask. Gdy jest napisane Enable, wówczas zatrzask jest nazywany przezroczystym, a sygnały rozprzestrzeniają się bezpośrednio przez niego, ponieważ nie jest obecny.

JEST | re | Q | Q ” |

0 | 0 | Zatrzask | Zatrzask |

0 | 1 | Zatrzask | Zatrzask |

1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Zamknięty zatrzask D.

DO zamykany zatrzask D. jest zaprojektowany po prostu przez zmianę zatrzasku bramkowanego SR, a jedyną zmianą w zatrzasku bramkowanym SR jest to, że wejście R musi zostać zmodyfikowane do odwróconego S. Zatrzask bramkowany nie może być utworzony z zatrzasku SR za pomocą NOR jest pokazany poniżej.

Zamknięty zatrzask D.

Zawsze, gdy CLK w innym przypadku jest włączone, jest wysokie, o / p zatrzaskuje wszystko, co jest na wejściu D. Podobnie, gdy CLK jest niskie, wtedy D i / p dla końcowego poziomu włączenia jest wyjściem.

CLK | re | Q (t + 1) |

| 0 | X | Q (t) |

1 | 0 | 0 |

| 1 | 1 | 1 |

Obwód zatrzasku w ogóle nie doświadczy stanu wyścigu, ponieważ jedyne wejście D jest odwrócone, aby oferować oba wejścia. Dlatego nie ma możliwości uzyskania podobnego stanu wejściowego. W ten sposób obwód zatrzasku typu D może być bezpiecznie używany w kilku obwodach.

JK Latch

Oboje Zatrzask JK , podobnie jak zatrzask RS, jest podobny. Ten zatrzask zawiera dwa wejścia, mianowicie J i K, które są pokazane na poniższym schemacie bramki logicznej. W tego typu zatrzasku stan niejasny został tutaj usunięty. Kiedy wejścia zatrzasku JK są w stanie wysokim, wyjście zostanie przełączone. Jedyną różnicą, jaką możemy tutaj zaobserwować, jest sprzężenie zwrotne wyjścia na wejścia, którego nie ma w zatrzasku RS.

JK Latch

T Latch

Plik Zatrzask T. może powstać, gdy wejścia zatrzasku JK są zwarte. Funkcja T Latch będzie taka, gdy wejście zatrzasku jest wysokie, a następnie wyjście zostanie przełączone.

T Latch

Zalety zatrzasków

Plik zalety zatrzasków obejmują następujące elementy.

- Projektowanie zatrzasków jest bardzo elastyczne w porównaniu z FFS (japonki)

- Zatrzaski zużywają mniej energii.

- Działanie zatrzasku w projekcie szybkiego obwodu jest szybkie, ponieważ są one asynchroniczne w projekcie i nie ma potrzeby stosowania sygnału CLK.

- Kształt zatrzasku jest bardzo mały i zajmuje mniej miejsca

- Jeśli działanie obwodu opartego na zatrzasku nie zakończy się w ustalonym czasie, pożyczają od innych czas niezbędny do zakończenia operacji

- Zatrzaski dają agresywne taktowanie w przeciwieństwie do obwody typu flip-flop .

Wady zatrzasków

Plik wady zatrzasków obejmują następujące elementy.

- Istnieje szansa wpłynięcia na stan wyścigu, więc są one mniej oczekiwane.

- Kiedy zatrzask jest wrażliwy na poziom, istnieje szansa na meta-stabilność.

- Analiza obwodu jest trudna ze względu na właściwość czułości na poziom.

- Obwód można przetestować za pomocą dodatkowego programu CAD

Zastosowanie zatrzasków

Plik zastosowania zatrzasków obejmują następujące elementy.

- Ogólnie rzecz biorąc, zatrzaski są używane do zachowania warunków bitów do kodowania liczb binarnych

- Zatrzaski to jednobitowe elementy pamięci, które są szeroko stosowane w obliczeniach, a także w przechowywaniu danych.

- Zatrzaski są używane w obwodach, takich jak bramkowanie mocy i zegar jako urządzenie magazynujące.

- Zatrzaski typu D mają zastosowanie w systemach asynchronicznych, takich jak porty wejściowe lub wyjściowe.

- Zatrzaski danych są używane w synchronicznych systemach dwufazowych w celu zmniejszenia liczby tranzytów.

A zatem chodzi o przegląd zamków. To są elementy składowe obwody sekwencyjne . Projektowanie tego można wykonać za pomocą bramek logicznych. Jego działanie zależy głównie od wejścia funkcji włączania. Oto pytanie do Ciebie, jakie są dwa stany pracy zatrzasków?