W dziedzinie elektroniki najważniejszą koncepcją, nad którą pracuje każdy komponent, jest „ Bramki logiczne „. Ponieważ koncepcja bramek logicznych jest realizowana w każdej funkcjonalności, takiej jak układy scalone, czujniki, cele przełączania, mikrokontrolery i procesory, cele szyfrowania i deszyfrowania i inne. Oprócz tego istnieje szerokie zastosowanie bramek logicznych. Istnieje wiele typów bramek logicznych, takich jak Adder, Subtractor, Full Sumator , Full Subtractor, Half Subtractor i wiele innych. Tak więc ten artykuł zawiera zbiorcze informacje o obwód pół odejmowania , pół odejmowana tabela prawdy i pokrewne pojęcia.

Co to jest Half Subtractor?

Zanim przejdziemy do pół odejmowania, musimy znać odejmowanie binarne. W odejmowaniu binarnym proces odejmowania jest podobny do odejmowania arytmetycznego. W odejmowaniu arytmetycznym używany jest system liczbowy o podstawie 2, podczas gdy w odejmowaniu binarnym liczby binarne są używane do odejmowania. Wynikowe warunki można oznaczyć jako różnicę i pożyczyć.

Najważniejszy jest pół odejmowanie kombinacyjny obwód logiczny który jest używany w Elektronika cyfrowa . Zasadniczo jest to urządzenie elektroniczne lub innymi słowy, możemy powiedzieć, że jest to obwód logiczny. Ten obwód służy do odejmowania dwóch cyfr binarnych. W poprzednim artykule omówiliśmy już koncepcje pół sumatora i pełnego obwodu sumatora który używa liczb binarnych do obliczeń. Podobnie obwód odejmowania używa liczb binarnych (0,1) do odejmowania. Obwód pół odejmowania można zbudować z dwóch bramki logiczne, mianowicie bramki NAND i EX-OR . Ten obwód daje dwa elementy, takie jak różnica, a także pożyczają.

Podobnie jak w odejmowaniu binarnym, główna cyfra to 1, możemy wygenerować pożyczkę, podczas gdy odjemnik 1 jest lepszy od odjemnego 0 i z tego powodu pożyczka będzie potrzebować. Poniższy przykład przedstawia binarne odejmowanie dwóch bitów binarnych.

Pierwsza cyfra | Druga cyfra | Różnica | Pożyczać |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

W powyższym odjęciu, dwie cyfry można przedstawić za pomocą A i B. Te dwie cyfry można odjąć i otrzymać wynikowe bity jako różnicę i pożyczkę.

Kiedy obserwujemy pierwsze dwa i czwarte wiersze, różnicę między tymi wierszami, to różnica i pożyczenie są podobne, ponieważ odjemnik jest mniejszy niż odjemnik. Podobnie, gdy obserwujemy trzeci wiersz, wartość odjemna jest odejmowana od odjemnika. Zatem bity różnicy i pożyczki wynoszą 1, ponieważ cyfra odjemna jest lepsza od cyfry odjemnej.

Ten układ kombinacyjny jest niezbędnym narzędziem do każdego rodzaju obwód cyfrowy poznanie możliwych kombinacji wejść i wyjść. Na przykład, jeśli odejmowanie ma dwa wejścia, wynikowe wyjścia będą wynosić cztery. O / p pół odejmowania jest wymienione w poniższej tabeli, która będzie oznaczać bit różnicy, a także bit pożyczki. Objaśnienie tabeli prawdy obwodu można wykonać za pomocą bramek logicznych, takich jak bramka logiczna EX-OR i operacja bramki AND, po której następuje bramka NOT.

Rozwiązywanie tabeli prawdy za pomocą Mapa K pokazano poniżej.

mapa pół odejmowania k

Plik wyrażenie pół odejmujące używając tabeli prawdy i mapy K można wyprowadzić jako

Różnica (D) = ( x'y + xy ')

= x ⊕ y

Pożycz (B) = x'y

Układ logiczny

Plik obwód logiczny pół odejmowania można wyjaśnić za pomocą bramek logicznych:

- 1 bramka XOR

- 1 NIE brama

- 1 AND brama

Reprezentacja jest

Obwód logiczny pół odejmowania

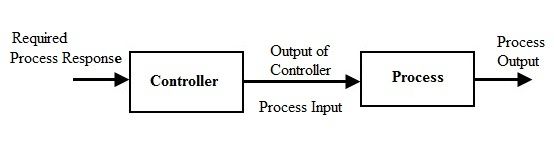

Schemat blokowy pół odejmowania

Schemat blokowy pół odejmowania pokazano powyżej. Wymaga dwóch wejść, a także daje dwa wyjścia. Tutaj dane wejściowe są reprezentowane przez A i B, a dane wyjściowe to Różnica i Pożycz.

Powyższy obwód można zaprojektować z bramkami EX-OR i NAND. Tutaj bramę NAND można zbudować za pomocą bramek AND i NOT. Potrzebujemy więc trzech bramek logicznych do wykonania połowy obwodu odejmującego, a mianowicie bramki EX-OR, bramki NOT i bramki NAND.

Kombinacja bramek AND i NOT tworzy inną połączoną bramkę o nazwie NAND Gate. Wyjście bramki Ex-OR będzie bitem różnicy, a wyjście bramki NAND będzie bitem pożyczki dla tych samych wejść A i B.

Bramka AND

Bramka AND jest jednym rodzajem cyfrowej bramki logicznej z wieloma wejściami i jednym wyjściem i na podstawie kombinacji wejść wykona logiczną koniunkcję. Gdy wszystkie wejścia tej bramki są w stanie wysokim, to wyjście będzie wysokie, w przeciwnym razie wyjście będzie niskie. Schemat logiczny bramki AND z tablicą prawdy pokazano poniżej.

AND Brama i tablica prawdy

NIE Brama

Bramka NOT jest rodzajem cyfrowej bramki logicznej z pojedynczym wejściem i na podstawie wejścia wyjście będzie odwrócone. Na przykład, gdy wejście bramki NOT jest wysokie, wtedy wyjście będzie niskie. Schemat logiczny bramki NOT z tablicą prawdy jest pokazany poniżej. Używając tego typu bramki logicznej, możemy wykonać bramki NAND i NOR.

NIE Brama i Tabela Prawdy

Brama Ex-OR

Bramka Exclusive-OR lub EX-OR to jeden rodzaj cyfrowej bramki logicznej z 2 wejściami i jednym wyjściem. Działanie tej bramki logicznej zależy od bramki OR. Jeśli którekolwiek z wejść tej bramki jest w stanie wysokim, to wyjście bramki EX-OR będzie wysokie. Symbol i tablica prawdy EX-OR są pokazane poniżej.

Brama XOR i tabela prawdy

Obwód pół odejmowania wykorzystujący bramkę Nand

Projektowanie odejmowania można wykonać za pomocą za pomocą bramek logicznych jak bramka NAND i bramka Ex-OR. Aby zaprojektować ten obwód pół odejmowania, musimy znać dwa pojęcia, a mianowicie różnicę i pożyczkę.

Obwód pół odejmowania wykorzystujący bramkę Nand

Jeśli uważnie monitorujemy, jest całkiem jasne, że różnorodność operacji wykonywanych przez ten obwód jest dokładnie związana z działaniem bramki EX-OR. Dlatego możemy po prostu użyć bramki EX-OR, aby coś zmienić. W ten sam sposób pożyczkę wytworzoną przez obwód półsumatora można po prostu uzyskać za pomocą połączenia bramek logicznych, takich jak bramka AND i bramka NIE.

Ten HS może być również zaprojektowany przy użyciu bramek NOR, gdzie wymaga 5 bramek NOR do budowy. Schemat obwodu pół odejmowania wykorzystujący bramki NOR jest pokazany jako:

Half Subtractor używający Nor Gates

Tabela prawdy

Pierwszy kawałek | Drugi bit | Różnica (EX-OR Out) | Pożyczać (Wyjście NAND) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Kod VHDL i Testbench

Kod VHDL dla pół odejmowania jest wyjaśniony w następujący sposób:

biblioteka IEEE

użyj IEEE.STD_LOGIC_1164.ALL

użyj IEEE.STD_LOGIC_ARITH.ALL

użyj IEEE.STD_LOGIC_UNSIGNED.ALL

Encja Half_Sub1 to

Port (a: w STD_LOGIC

b: w STD_LOGIC

HS_Diff: out STD_LOGIC

HS_Borrow: obecnie STD_LOGIC)

koniec Half_Sub1

architektura Zachowanie Half_Sub1 to

zaczynać

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

Plik kod testbench dla HS wyjaśniono jak poniżej:

LIBRARY IEEE

UŻYJ ieee.std_logic_1164.ALL

ENTITY HS_tb IS

KONIEC HS_tb

ARCHITEKTURA HS_tb Z HS_tb JEST

COMPONENT HS

PORT (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

KOMPONENT KOŃCOWY

signal a: std_logic: = „0”

sygnał b: std_logic: = „0”

sygnał HS_Diff: std_logic

sygnał HS_Borrow: std_logic

ZACZYNAĆ

nowość: MAPA PORTU HS (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: proces

zaczynać

do<= ‘0’

b<= ‘0’

poczekaj 30 ns

do<= ‘0’

b<= ‘1’

poczekaj 30 ns

do<= ‘1’

b<= ‘0’

poczekaj 30 ns

do<= ‘1’

b<= ‘1’

czekać

koniec procesu

KONIEC

Pełny odejmowanie przy użyciu pół odejmowania

Odejmowanie pełne to urządzenie kombinacyjne, które obsługuje funkcję odejmowania za pomocą dwóch bitów i jest odejmowane i odejmowane. Obwód bierze pod uwagę pożyczenie poprzedniego wyjścia i ma trzy wejścia z dwoma wyjściami. Trzy dane wejściowe to odejście, odliczenie i dane wejściowe otrzymane z poprzedniego wyniku, który jest pożyczany, a dwa wyjścia to różnica i pożyczka.

Pełny diagram logiczny odejmowania

Tabela prawdy dla pełny odejmowanie jest

| Wejścia | Wyjścia | |||

| X | Y | Yin | FS_Diff | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Z powyższą tabelą prawdy, schemat logiczny i schemat obwodów dla implementacji pełnego odejmowania przy użyciu pół odejmowania jest pokazany poniżej:

Pełny odejmowanie przy użyciu HS

Zalety i ograniczenia Half Subtractor

Zalety pół odejmowania to:

- Realizacja i konstrukcja tego układu jest prosta i łatwa

- Ten obwód zużywa minimalną moc podczas cyfrowego przetwarzania sygnału

- funkcje obliczeniowe można wykonywać z większą szybkością

Ograniczenia tego układu kombinacyjnego to:

Chociaż istnieje wiele zastosowań pół odejmowania w wielu operacjach i funkcjach, istnieje kilka ograniczeń, a są to:

- Obwody półodejmujące nie akceptują „wypożyczenia” z poprzednich wyjść, gdzie jest to kluczowa wada tego obwodu

- Ponieważ wiele aplikacji czasu rzeczywistego działa na odejmowaniu wielu bitów, urządzenia półodejmujące nie mają żadnej możliwości odejmowania wielu bitów

Zastosowania Half Subtractor

Zastosowania pół odejmowania obejmują następujące elementy.

- Pół odejmowanie służy do zmniejszenia siły sygnałów audio lub radiowych

- To może być stosowany we wzmacniaczach aby zredukować zniekształcenia dźwięku

- Odejmowanie połowy to używany w ALU procesora

- Może być używany do zwiększania i zmniejszania operatorów, a także oblicza adresy

- Pół odejmowanie służy do odejmowania najmniej znaczących liczb kolumn. Do odejmowania liczb wielocyfrowych można go użyć dla LSB.

Dlatego z powyższej teorii półodejmowania w końcu możemy zamknąć to, używając tego obwodu, możemy odjąć od jednego bitu binarnego od drugiego, aby uzyskać wyniki takie jak różnica i pożyczka. Podobnie możemy zaprojektować pół odejmowanie wykorzystując obwód bramek NAND, a także bramki NOR. Inne pojęcia, które należy poznać, to to, co to jest kod verilog pół odejmowania i jak można narysować schematyczny diagram RTL?