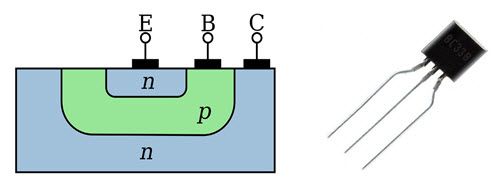

ECL (logika sprzężona z emiterem) została po raz pierwszy wynaleziona w IBM w sierpniu 1956 roku przez Hannona S. Yourke'a. Ta logika jest również znana jako logika trybu prądu, używana w komputerach IBM 7090 i 7094. Rodzina ECL jest bardzo szybka w porównaniu do logika cyfrowa rodziny. Ogólnie rzecz biorąc, ta rodzina logiki zapewnia opóźnienie propagacji mniejsze niż 1 ns. Jest to rodzina logiki oparta na bipolarnych tranzystorach złączowych. Jest to najszybszy obwód rodziny układów logicznych, który jest dostępny do projektowania konwencjonalnego systemu logicznego. W tym artykule omówiono omówienie układ logiczny sprzężony z emiterem , praca z aplikacjami.

Co to jest logika sprzężona z emiterem?

Logika sprzężona z emiterem jest najlepsza BJT oparta na rodzinie logiki używana w konwencjonalnym projektowaniu systemów logicznych. Czasami nazywa się to również logiką trybu prądu, która jest bardzo szybką technologią cyfrową. Ogólnie rzecz biorąc, ECL jest uważany za najszybszy układ logiczny, w którym osiąga swoje szybkie działanie dzięki bardzo małym wahaniom napięcia i unikaniu wejścia tranzystorów w obszar nasycenia.

Implementacja ECL wykorzystuje dodatnie napięcie zasilania, które jest znane jako PECL lub ECL z dodatnią referencją. We wczesnych bramkach ECL stosuje się ujemne napięcie zasilania ze względu na odporność na zakłócenia. Następnie ECL z dodatnim odniesieniem stał się bardzo sławny ze względu na bardziej kompatybilne poziomy logiczne w porównaniu do rodzin logicznych TTL.

Logika sprzężona z emiterem rozprasza ogromną ilość mocy statycznej, jednak jej ogólny pobór prądu jest niski w porównaniu do CMOS przy wysokich częstotliwościach. Tak więc ECL jest szczególnie korzystny w obwodach dystrybucji zegara i aplikacjach opartych na wysokich częstotliwościach.

Funkcje logiki sprzężonej z emiterem

Cechy ECL sprawią, że będą one używane w wielu aplikacjach o wysokiej wydajności.

- ECL zapewnia dwa wyjścia, które zawsze się uzupełniają, ponieważ działanie układu oparte jest na wzmacniaczu różnicowym.

- Ta rodzina układów logicznych nadaje się głównie do monolitycznych metod wytwarzania, ponieważ poziomy logiczne są funkcją współczynników rezystorów.

- Urządzenia z rodziny ECL generują właściwe i uzupełniające wyjście proponowanej funkcji bez użycia zewnętrznych falowników. W konsekwencji zmniejsza liczbę pakietów i wymagania dotyczące mocy, a także zmniejsza problemy wynikające z opóźnień czasowych.

- Urządzenia ECL w konstrukcji wzmacniacza różnicowego oferują szeroką elastyczność działania, dzięki czemu obwody ECL mogą być stosowane zarówno jako obwody cyfrowe, jak i liniowe.

- Konstrukcja bramki ECL ma zwykle wysoką i niską impedancję wejściową, co bardzo sprzyja osiągnięciu dużego rozgałęzienia, a także możliwości napędu.

- Urządzenia ECL generują stały pobór prądu na zasilaczu, aby uprościć konstrukcję zasilacza.

- Urządzenia ECL, w tym wyjścia otwartego emitera, pozwalają po prostu na uwzględnienie wydajności napędu linii transmisyjnej.

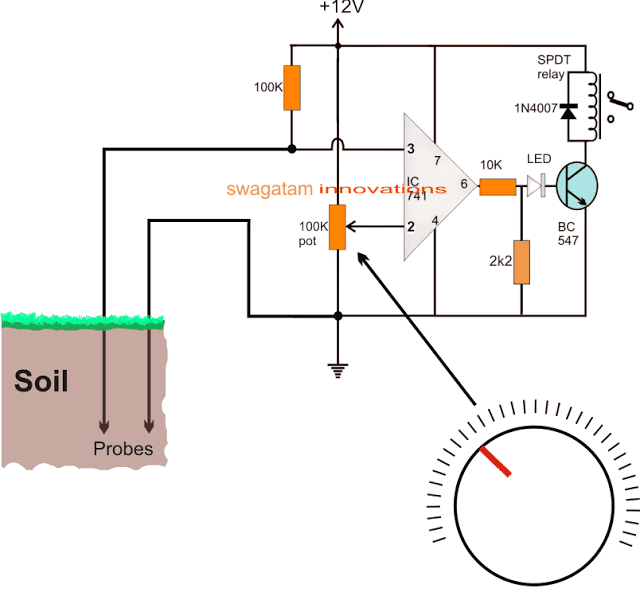

Obwód logiczny sprzężony z emiterem

Poniżej pokazano obwód logiczny falownika sprzężony z emiterem, który jest zaprojektowany z rezystorami i tranzystorami. W tym obwodzie zaciski emitera dwóch tranzystorów są po prostu połączone z rezystancją ograniczającą prąd RE, która służy do uniknięcia nasycenia tranzystora. Tutaj wyjście tranzystora jest pobierane z zacisku kolektora zamiast zacisku emitera. Ten obwód zapewnia dwa wyjścia Vout (wyjście odwracające) i Vout2 (wyjście nieodwracające) oraz terminal wejściowy, taki jak Vin, gdzie podany jest wysoki lub niski sygnał wejściowy. +Vcc = 5V.

Jak działa logika sprzężona z emiterem?

Działanie logiki sprzężonej z emiterem polega na tym, że każde podanie wejścia HIGH do układu ECL spowoduje włączenie tranzystora „Q1” i wyłączenie tranzystora Q2, ale tranzystor Q1 nie jest nasycony. Więc spowoduje to, że wyjście VOUT2 będzie WYSOKIE, a wartość wyjścia VOUT1 będzie NISKA z powodu spadku w R1.

Podobnie, gdy wartość VIN podana do ECL jest NISKA, spowoduje to wyłączenie tranzystora Q1 i włączenie tranzystora Q2. Tak więc tranzystor Q2 nie przejdzie w nasycenie. Więc spowoduje to, że wyjście VOUT1 zostanie wyciągnięte na WYSOKĄ wartość, a wartość wyjściowa VOUT2 będzie niska z powodu spadku rezystancji R2.

Zobaczmy, jak tranzystory Q1 i Q2 włączają się i wyłączają po przyłożeniu napięcia.

Dwa tranzystory, takie jak Q1 i Q2 w tym obwodzie, są połączone jako wzmacniacz różnicowy za pomocą wspólnego rezystora emiterowego.

Zasilanie napięciowe dla tego przykładowego obwodu to VCC = 5,0, VBB = 4,0 i VEE = 0 V. Wejściowe wartości wysokiego i niskiego poziomu są po prostu zdefiniowane jako 4,4 V i 3,6 V. W rzeczywistości obwód ten generuje NISKĄ moc wyjściową i WYSOKIE poziomy, które są o 0,6 V wyższe; jest to jednak korygowane w rzeczywistych obwodach ECL.

Gdy Vin jest WYSOKIE, tranzystor Q1 jest włączony, ale nie jest nasycony, a tranzystor Q2 jest wyłączony. Tak więc napięcie wyjściowe, takie jak VOUT2 jest podciągane do 5 V przez rezystor R2 i można wykazać, że spadek napięcia na rezystorze R1 wynosi około 0,8 V, więc VOUT1 = 4,2 V (NISKI). Dodatkowo VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, ponieważ tranzystor Q1 jest całkowicie włączony.

Gdy Vin będzie LOW, tranzystor Q2 zostanie włączony, ale nie będzie nasycony, a tranzystor Q1 zostanie wyłączony. Dlatego VOUT1 jest podciągnięty do 5,0 V za pomocą rezystora R1 i można wykazać, że VOUT2 wynosi 4,2 V. Również VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, gdy tranzystor Q2 jest włączony.

W ECL dwa tranzystory nigdy nie są nasycone jak t Wahania napięcia wejściowego / wyjściowego są dość małe, jak 0,8 V a impedancja wejściowa jest wysoka, a rezystancja wyjściowa jest niska. Pomaga to ECL działać szybciej przy krótszym czasie opóźnienia propagacji.

Obwód bramki logicznej OR/NOR ze sprzężeniem z dwoma wejściami i emiterem

Obwód bramki logicznej OR/NOR z dwoma wejściami i emiterem pokazano poniżej. Ten obwód został zaprojektowany przez modyfikację powyższego obwodu falownika. Modyfikacja polega na dodaniu dodatkowego tranzystora po stronie wejściowej.

Działanie tego obwodu jest bardzo proste. Gdy wejścia zastosowane na obu tranzystorach Q1 i Q2 są niskie, wówczas wyjście 1 (Vout1) będzie miało wartość WYSOKA. Tak więc ten Vout1 odpowiada wyjściu bramki NOR.

Jednocześnie, jeśli tranzystor Q3 jest włączony, spowoduje to, że drugie wyjście (Vout2) będzie WYSOKIE. Tak więc to wyjście Vou2 odpowiada wyjściu bramki OR.

W ten sam sposób, jeśli oba wejścia tranzystorów Q1 i Q2 są WYSOKIE, to włączy tranzystory Q1 i Q2 i dostarczy niski sygnał wyjściowy na zacisku VOUT1.

Jeśli tranzystor Q3 jest wyłączony podczas tej operacji, to zapewni wysoki sygnał wyjściowy na zacisku VOUT2. Tak więc tabela prawdy dla bramki OR/NOR jest podana poniżej.

|

Wejścia |

Wejścia | LUB |

ANI |

|

A |

B | Tak | Tak |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Charakterystyka logiczna sprzężona z emiterem

Cechy charakterystyczne ECL obejmują następujące elementy.

- W porównaniu do TTL, ECL ma szybszy czas propagacji w zakresie od 0,5 do 2 ns. Ale rozpraszanie mocy logicznej sprzężonej z emiterem jest wyższe w porównaniu do TTL, np. 30 mW.

- Napięcia we/wy ECL mają niewielkie wahania, takie jak 0,8.

- Impedancja wejściowa ECL jest wysoka, a rezystancja wyjściowa niska; w konsekwencji tranzystor bardzo szybko zmienia swoje stany.

- Wydajność rozgałęzienia ECL jest wysoka, a opóźnienia bramek niskie.

- Logika o/p ECL zmienia się ze stanu NISKIEGO na WYSOKI, ale poziomy napięcia dla tych stanów będą się różnić między TTL i EC.

- Odporność na zakłócenia ECL wynosi 0,4V.

Zalety i wady

The zalety logiki sprzężonej z emiterem są omówione poniżej.

- Fanout ECL wynosi 25, co jest lepsze w porównaniu z TTL i jest niskie w porównaniu z CMOS.

- Średni czas opóźnienia propagacji ECL wynosi od 1 do 4 ns, co jest lepsze w porównaniu z CMOS i

- TTL. Dlatego nazywana jest najszybszą rodziną logiczną.

- Kiedy BJT w emiterze są połączone bramki logiczne pracują w aktywnym regionie, wtedy mają maksymalną prędkość w porównaniu do wszystkich rodzin logicznych.

- Bramki ECL generują wyjścia komplementarne.

- W przewodach zasilających nie ma szpilek przełączających prąd.

- Wyjścia mogą być połączone razem, aby zapewnić funkcję przewodowego OR.

- Parametry ECL nie zmieniają się znacząco pod wpływem temperatury.

- Nie. funkcji dostępnych z jedynego chipa jest wysoka.

The wady logiki sprzężonej z emiterem są omówione poniżej.

- Ma ekstremalnie mniejszy margines szumów, tj. ±200 mV.

- Rozpraszanie mocy jest wysokie w porównaniu do innych bramek logicznych.

- Aby połączyć się z innymi rodzinami logiki, konieczne są przełączniki poziomów.

- Fanout ogranicza ładowanie pojemnościowe.

- W porównaniu do TTL , bramki ECL są drogie.

- W porównaniu do CMOS i TTL odporność na zakłócenia ECL jest najgorsza.

Aplikacje

Zastosowania logiki sprzężonej z emiterem obejmują następujące.

- Logika sprzężona z emiterem jest wykorzystywana jako technologia logiki i interfejsu w bardzo szybkich urządzeniach komunikacyjnych, takich jak światłowodowe interfejsy nadawczo-odbiorcze, sieci Ethernet i ATM (tryb transmisji asynchronicznej).

- ECL to rodzina układów logicznych oparta na BJT, w której jej szybkie działanie można osiągnąć, stosując stosunkowo niewielkie wahania napięcia i unikając przesuwania się tranzystorów w obszar nasycenia.

- ECL jest używany do tworzenia obwodów ASLT w IBM 360/91.

- ECL pozwala uniknąć wykorzystania tranzystorów ułożonych w stos dzięki zastosowaniu jednokierunkowego polaryzacji i/p i dodatniego sprzężenia zwrotnego między tranzystorami pierwotnymi i wtórnymi w celu uzyskania funkcji falownika.

- ECL jest używany w elektronice o bardzo dużej szybkości.

Tak więc jest to przegląd logiki sprzężonej z emiterem lub ECL – obwód, działanie, cechy, charakterystyki i zastosowania. ECL to najszybsza rodzina układów logicznych oparta na BJT w porównaniu z innymi rodzinami układów cyfrowych. Osiąga maksymalną prędkość działania, stosując niewielkie wahania napięcia i unikając przesuwania się tranzystorów w obszar nasycenia. Ta rodzina układów logicznych zapewnia niewiarygodne opóźnienie propagacji 1 ns, aw najnowszych rodzinach ECL opóźnienie to jest zmniejszone. Oto pytanie do Ciebie, jaka jest alternatywna nazwa ECL?