Do wykonania programu komputerowego wymaga synchronicznej pracy więcej niż jednego elementu komputera. Na przykład, Procesory - dostarczanie niezbędnych informacji sterujących, adresów… itd., Szyny - do przesyłania informacji i danych do iz pamięci do urządzeń I / O… itd. Interesującym czynnikiem systemu byłby sposób, w jaki obsługuje on przesyłanie informacji między procesorem, pamięcią i urządzeniami we / wy. Zwykle procesory kontrolują cały proces przesyłania danych, począwszy od zainicjowania transferu, a skończywszy na przechowywaniu danych w miejscu docelowym. Zwiększa to obciążenie procesora i przez większość czasu pozostaje w idealnym stanie, zmniejszając w ten sposób wydajność systemu. Aby przyspieszyć przesyłanie danych między urządzeniami I / O a pamięcią, kontroler DMA działa jako stacja master. Kontroler DMA przesyła dane przy minimalnej interwencji procesora.

Co to jest kontroler DMA?

Termin DMA oznacza bezpośredni dostęp do pamięci. Urządzenie sprzętowe używane do bezpośredniego dostępu do pamięci nazywane jest kontrolerem DMA. DMA Kontroler to jednostka sterująca , część urządzeń we / wy obwód interfejsu , który może przesyłać bloki danych między urządzeniami we / wy a pamięcią główną przy minimalnej interwencji procesora.

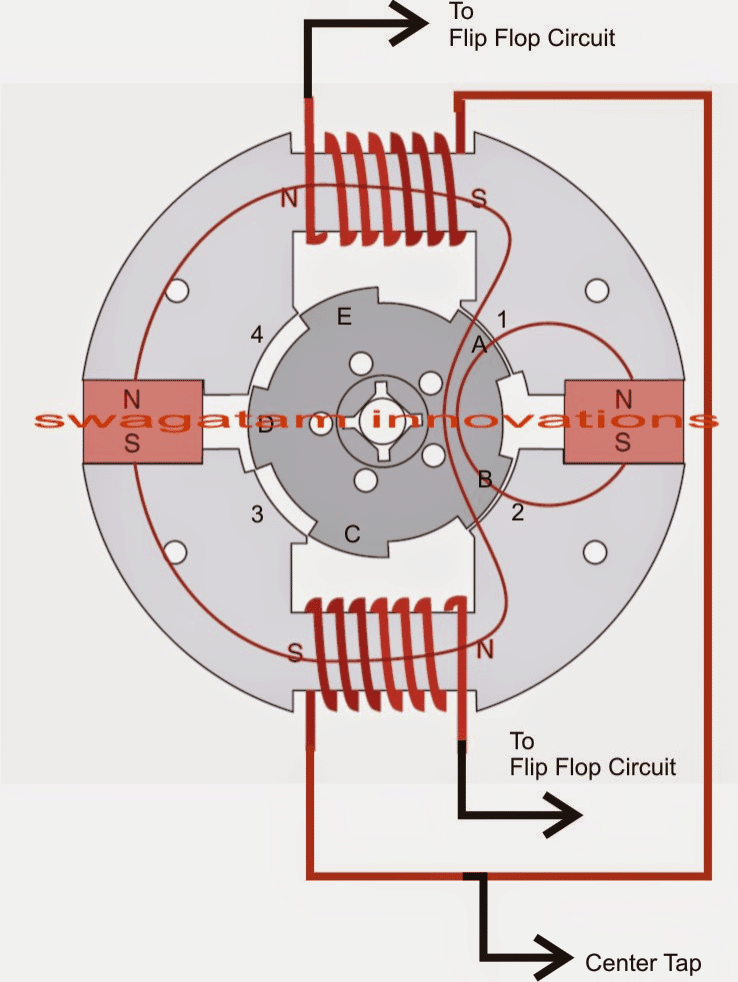

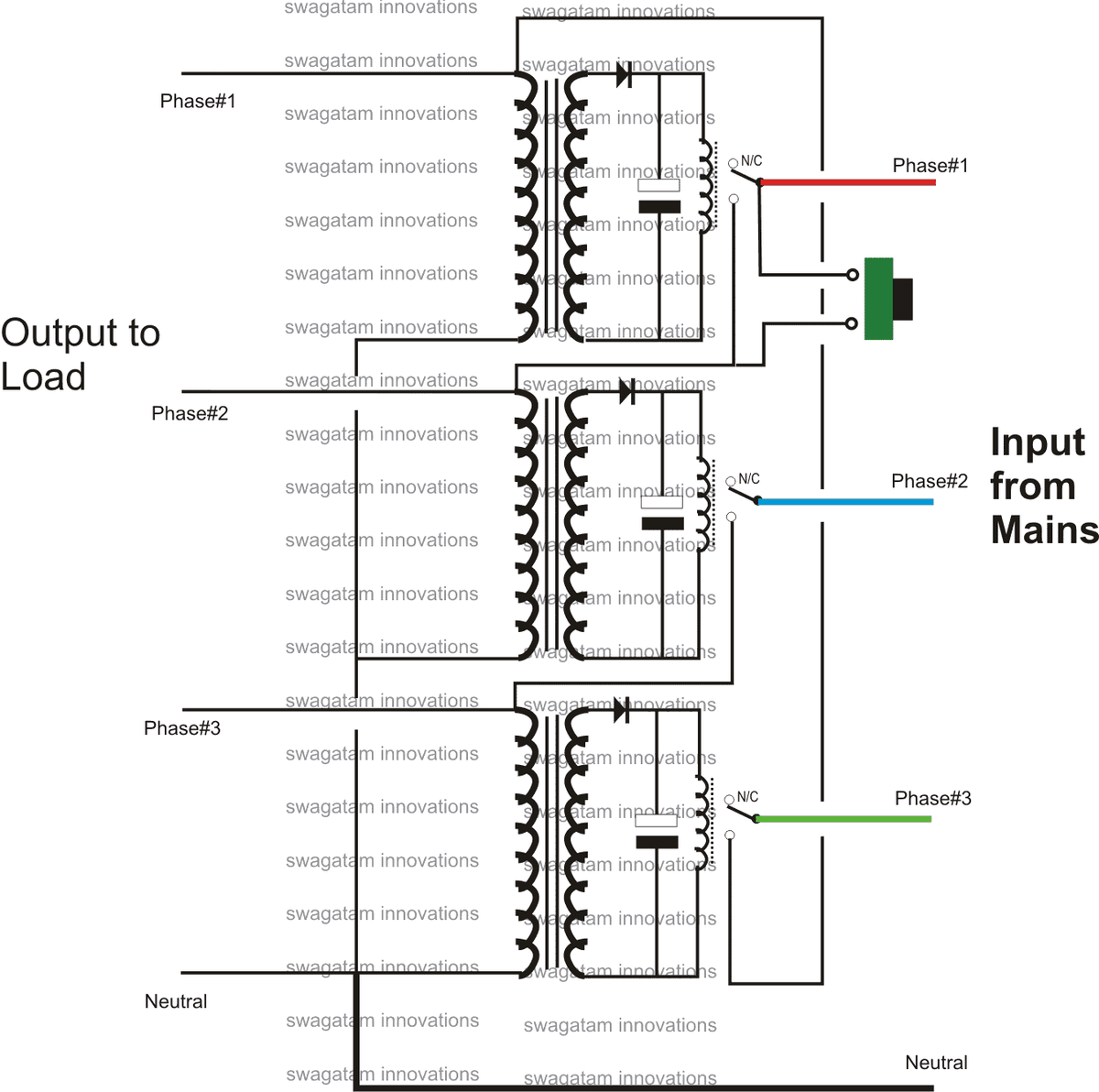

Schemat kontrolera DMA w architekturze komputerów

Kontroler DMA zapewnia interfejs między magistralą a urządzeniami wejścia-wyjścia. Chociaż przesyła dane bez interwencji procesora, jest kontrolowany przez procesor. Procesor inicjuje kontroler DMA wysyłając adres początkowy, liczbę słów w bloku danych i kierunek przesyłania danych, tj. z urządzeń we / wy do pamięci lub z pamięci głównej do urządzeń we / wy. Do kontrolera DMA można podłączyć więcej niż jedno urządzenie zewnętrzne.

DMA w architekturze komputerów

Kontroler DMA zawiera jednostkę adresową do generowania adresów i wyboru urządzenia I / O do transferu. Zawiera również jednostkę sterującą i licznik danych do zliczania liczby przesłanych bloków i wskazania kierunku przesyłania danych. Po zakończeniu przesyłania, DMA informuje procesor, podnosząc przerwanie. Typowy schemat blokowy kontrolera DMA pokazano na poniższym rysunku.

Typowy schemat blokowy kontrolera DMA

Działanie kontrolera DMA

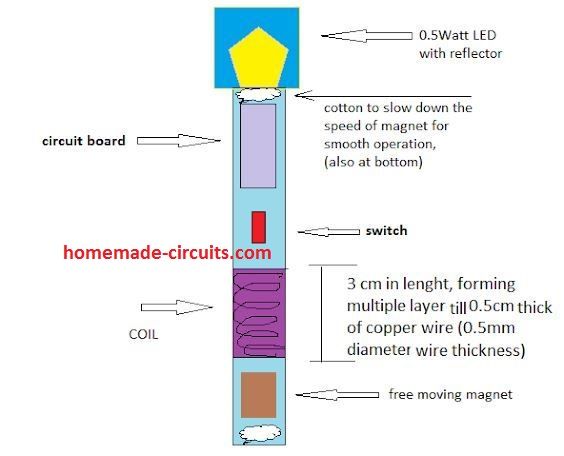

Kontroler DMA musi współdzielić magistralę z procesorem, aby umożliwić transfer danych. Urządzenie, które utrzymuje magistralę w określonym czasie, nazywa się Bus Master. Kiedy trzeba wykonać transfer z urządzenia we / wy do pamięci lub odwrotnie, procesor zatrzymuje wykonywanie bieżącego programu, zwiększa program licznik, przenosi dane na stos, a następnie wysyła sygnał wyboru DMA do kontrolera DMA przez szynę adresową.

Jeśli kontroler DMA jest wolny, żąda sterowania magistralą od procesora, podnosząc sygnał żądania magistrali. Procesor przyznaje magistralę kontrolerowi, podnosząc sygnał przyznania magistrali, teraz kontroler DMA jest nadrzędnym magistralą. Procesor inicjuje kontroler DMA wysyłając adresy pamięci, liczbę bloków danych do przesłania oraz kierunek przesyłania danych. Po przypisaniu zadania przesyłania danych do kontrolera DMA, zamiast idealnie czekać na zakończenie przesyłania danych, procesor wznawia wykonywanie programu po pobraniu instrukcji ze stosu.

Transfer danych do komputera przez kontrolera DMA

Kontroler DMA ma teraz pełną kontrolę nad magistralami i może współpracować bezpośrednio z pamięcią i urządzeniami we / wy niezależnie od procesora. Dokonuje transferu danych zgodnie z instrukcjami sterującymi otrzymanymi przez procesor. Po zakończeniu transferu danych wyłącza sygnał żądania magistrali, a procesor wyłącza sygnał przyznania magistrali, przenosząc tym samym sterowanie magistralami do procesora.

Gdy urządzenie I / O chce zainicjować transfer, wysyła sygnał żądania DMA do kontrolera DMA, który kontroler potwierdza, czy jest wolny. Następnie kontroler żąda od procesora magistrali, podnosząc sygnał żądania magistrali. Po odebraniu sygnału przyznania magistrali przesyła dane z urządzenia. W przypadku n kanałowego kontrolera DMA można podłączyć n liczbę urządzeń zewnętrznych.

DMA przesyła dane w trzech trybach, które obejmują następujące.

do) Tryb zdjęć seryjnych : W tym trybie DMA przekazuje magistrale do CPU dopiero po zakończeniu całego transferu danych. W międzyczasie, jeśli procesor wymaga magistrali, musi pozostać idealny i czekać na transfer danych.

b) Cykl kradzieży trybu : W tym trybie DMA przekazuje sterowanie magistralami do CPU po przesłaniu każdego bajtu. Ciągle wysyła żądanie sterowania magistralą, przesyła jeden bajt i zwraca magistralę. Dzięki temu procesorowi nie musi długo czekać, jeśli potrzebuje magistrali do zadań o wyższym priorytecie.

do) Tryb przezroczysty: Tutaj DMA przesyła dane tylko wtedy, gdy CPU wykonuje instrukcję, która nie wymaga użycia szyn.

8237 Kontroler DMA

- 8237 ma 4 kanały we / wy wraz z elastycznością zwiększania liczby kanałów.

- Każdy kanał może być programowany indywidualnie i ma 64k adresu i możliwości przesyłania danych.

- Blok sterowania taktowaniem, blok sterowania poleceniami programu, blok enkodera priorytetów to trzy główne bloki 8237A.

- Wewnętrzne taktowanie i zewnętrzne sygnały sterujące są sterowane przez blok sterowania taktowaniem.

- Różne polecenia wydawane przez mikroprocesor do DMA są dekodowane przez blok sterowania poleceniami programu.

- Który kanał ma mieć najwyższy priorytet, decyduje priorytet blok enkodera .

8237A ma 27 wewnętrznych rejestrów.

8237A działa w dwóch cyklach - idealnym cyklu i cyklu aktywnym, gdzie każdy cykl zawiera 7 oddzielnych stanów składających się z jednego okresu zegara.

S0 - pierwszy stan, w którym kontroler zażądał połączenia z magistralą i oczekuje na potwierdzenie od procesora.

S1, S2, S3, S4 nazywane są stanami roboczymi 8237A, w których ma miejsce faktyczny transfer danych. Jeśli potrzeba więcej czasu na przesłanie stanów oczekiwania, SW są dodawane między tymi stanami.

W przypadku transferu z pamięci do pamięci muszą być wykonane transfery odczytu z pamięci i zapisu do pamięci. Pojedynczy transfer wymaga ośmiu stanów. Pierwsze cztery stany z indeksami dolnymi S11, S12, S13, S14 wykonują transfer odczytu z pamięci, a kolejne cztery S21, S22, S23, S24 służą do przesyłania danych do pamięci.

DMA przechodzi w stan idealny, gdy żaden kanał nie żąda usługi i nie wykonuje stanu SI. SI to stan nieaktywny, w którym DMA jest nieaktywny, dopóki nie otrzyma żądania. W tym stanie DMA jest w stanie programowym, w którym procesor może zaprogramować DMA.

Gdy DMA jest w idealnym stanie i nie otrzymuje dalszych żądań kanału, wysyła sygnał HRQ do procesora i przechodzi w stan aktywny, w którym może rozpocząć przesyłanie danych w trybie impulsowym, trybie kradzieży cyklu lub trybie przezroczystym.

Schemat pinów 8237

8257 Kontroler DMA

W połączeniu z jednym urządzeniem z portem I / O Intel 8212 kontroler 8257 DMA tworzy kompletny 4-kanałowy Kontroler DMA . Po otrzymaniu żądania transferu kontroler 8257-

- Przejmuje kontrolę nad magistralą systemową od procesora.

- Urządzenie peryferyjne podłączone do kanału o najwyższym priorytecie jest potwierdzane.

- Najmniej znaczące bity adresu pamięci są przenoszone przez linie adresowe A0-A7 magistrali systemowej.

- Najbardziej znaczące 8 bitów adresu pamięci są kierowane do portu 8212 I / O przez linie danych.

- Generuje odpowiednie sygnały sterujące do przesyłania danych między urządzeniami peryferyjnymi a adresowanymi lokalizacjami pamięci.

- Gdy określona liczba bajtów zostanie przesłana, kontroler informuje procesor o końcu transferu, aktywując wyjście licznika terminali (TC).

Na każdy kanał 8257 zawiera dwa Rejestry 16-bitowe - 1) Rejestr adresów DMA i 2) Rejestr licznika terminali, który powinien zostać zainicjowany przed włączeniem kanału. Adres pierwszej komórki pamięci, do której ma się uzyskać dostęp, jest ładowany do rejestru adresów DMA. 14 bitów niższego rzędu wartości załadowanej do rejestru licznika terminali wskazuje liczbę cykli DMA minus jeden przed aktywacją wyjścia licznika terminali. Rodzaj operacji dla kanału wskazują dwa najbardziej znaczące bity rejestru licznika terminala.

Schemat pinów 8257

Zalety i wady kontrolera DMA

Zalety i wady kontrolera DMA obejmują następujące elementy.

Zalety

- DMA przyspiesza operacje pamięci, pomijając udział procesora.

- Zmniejsza się obciążenie procesora.

- Do każdego transferu wystarczy kilka cykli zegara

Niedogodności

- Problem ze spójnością pamięci podręcznej można zauważyć, gdy do przesyłania danych jest używane DMA.

- Zwiększa cenę systemu.

DMA ( Bezpośredni dostęp do pamięci ) kontroler jest używany w kartach graficznych, kartach sieciowych, kartach dźwiękowych itp. DMA jest również używany do transferu wewnątrz chipa w procesorach wielordzeniowych. Działając w jednym z trzech trybów, DMA może znacznie zmniejszyć obciążenie procesora. W którym z trybów DMA pracowałeś? Który z trybów uważasz za skuteczniejszy?