Tranzystor MOS jest najbardziej podstawowym elementem w projektowaniu układów scalonych na dużą skalę. Tranzystory te są ogólnie podzielone na dwa typy PMOS i NMOS. Połączenie tranzystorów NMOS i PMOS jest znane jako a Tranzystor CMOS . Inny bramki logiczne & inne cyfrowe urządzenia logiczne, które są zaimplementowane, muszą mieć logikę PMOS. Ta technologia jest niedroga i ma dobrą odporność na zakłócenia. W tym artykule omówiono jeden z typów tranzystorów MOS, taki jak tranzystor PMOS.

Co to jest tranzystor PMOS?

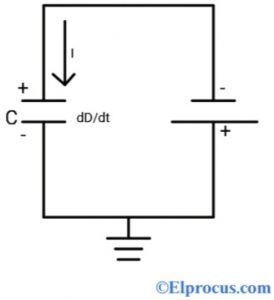

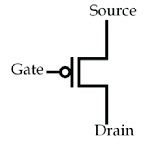

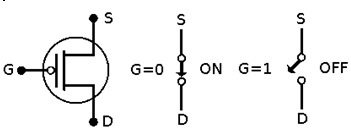

Tranzystor PMOS lub półprzewodnik z tlenkiem metalu z kanałem P jest rodzajem tranzystora, w którym domieszki typu p są wykorzystywane w kanale lub obszarze bramki. Ten tranzystor jest dokładnie odwrotnością tranzystora NMOS. Tranzystory te mają trzy główne zaciski; źródło, bramka i dren, gdzie źródło tranzystora jest zaprojektowane z podłożem typu p, a końcówka drenu jest zaprojektowana z podłożem typu n. W tym tranzystorze nośniki ładunku, takie jak dziury, odpowiadają za przewodzenie prądu. Symbole tranzystorów PMOS pokazano poniżej.

Jak działa tranzystor PMOS?

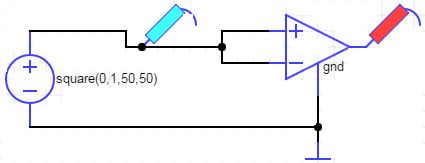

Tranzystor typu p działa zupełnie odwrotnie niż tranzystor typu n. Tranzystor ten utworzy obwód otwarty za każdym razem, gdy otrzyma nieistotne napięcie, co oznacza, że nie ma przepływu prądu z zacisku bramki (G) do źródła (S). Podobnie, ten tranzystor tworzy obwód zamknięty, gdy otrzymuje napięcie około 0 woltów, co oznacza, że prąd płynie od zacisku bramki (G) do drenu (D).

Ta bańka jest również znana jako bańka inwersyjna. Tak więc główną funkcją tego okręgu jest odwrócenie wartości napięcia wejściowego. Jeśli zacisk bramki dostarcza napięcie 1, wówczas ten falownik zmieni je na zero i odpowiednio uruchomi obwód. Tak więc funkcja tranzystora PMOS i tranzystora NMOS jest zupełnie odwrotna. Gdy połączymy je w jeden obwód MOS, stanie się on obwodem CMOS (komplementarny półprzewodnik z tlenku metalu).

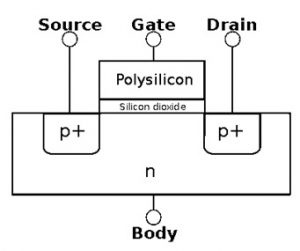

Przekrój tranzystora PMOS

Poniżej przedstawiono przekrój tranzystora PMOS. Tranzystor pMOS jest zbudowany z korpusu typu n, zawierającego dwa obszary półprzewodnikowe typu p, które sąsiadują z bramką. Ten tranzystor ma bramkę kontrolną, jak pokazano na schemacie, która kontroluje przepływ elektronów między dwoma zaciskami, takimi jak źródło i dren. W tranzystorze pMOS ciało jest utrzymywane pod napięciem +ve. Gdy zacisk bramki jest dodatni, zaciski źródła i drenu są spolaryzowane zaporowo. Gdy to nastąpi, nie będzie przepływu prądu, więc tranzystor zostanie WYŁĄCZONY.

Gdy napięcie zasilania na zacisku bramki zostanie obniżone, dodatnie nośniki ładunku zostaną przyciągnięte do dolnej części interfejsu Si-SiO2. Ilekroć napięcie spadnie wystarczająco nisko, kanał zostanie odwrócony i utworzy ścieżkę przewodzącą od zacisku źródłowego do drenu, umożliwiając przepływ prądu.

Ilekroć te tranzystory mają do czynienia z logiką cyfrową, zwykle mają dwie różne wartości, takie jak 1 i 0 (ON i OFF). Dodatnie napięcie tranzystora jest znane jako VDD, które reprezentuje wysoką wartość logiczną (1) w obwodach cyfrowych. Poziomy napięcia VDD w Logika TTL były na ogół około 5V. Obecnie tranzystory nie są w stanie wytrzymać tak wysokich napięć, ponieważ zwykle mieszczą się one w zakresie od 1,5 V do 3,3 V. Niskie napięcie jest często określane jako GND lub VSS. Tak więc VSS oznacza logiczne „0” i jest również ustawione normalnie na 0 V.

Obwód tranzystorowy PMOS

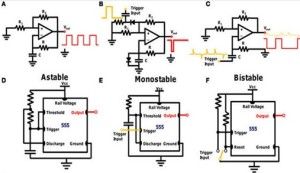

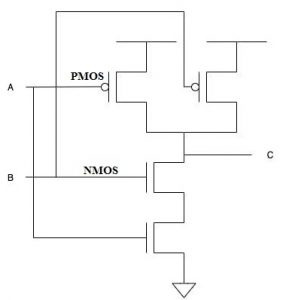

Projekt bramki NAND wykorzystującej tranzystor PMOS i tranzystor NMOS pokazano poniżej. Ogólnie rzecz biorąc, bramka NAND w elektronice cyfrowej jest bramką logiczną, zwaną również bramką NOT-AND. Wyjście tej bramki jest niskie (0) tylko wtedy, gdy dwa wejścia są wysokie (1), a jej wyjście jest uzupełnieniem bramki AND. Jeśli którekolwiek z dwóch wejść ma wartość NISKĄ (0), daje to wysokie wyniki wyjściowe.

W poniższym obwodzie logicznym, jeśli wejście A to 0, a B to 0, to wejście pMOS wygeneruje „1”, a wejście nMOS wytworzy „0”. Tak więc ta bramka logiczna generuje logiczne „1”, ponieważ jest połączona ze źródłem przez obwód zamknięty i odłączona od GND przez obwód otwarty.

Kiedy A to „0”, a B” to „1”, wtedy wejście pMOS wygeneruje „1”, a wejście NMOS wygeneruje „0”. W ten sposób ta bramka wytworzy logiczną, ponieważ jest podłączona do źródła przez obwód zamknięty i odłączona od GND przez obwód otwarty. Kiedy A to „1”, a B to „0”, wówczas wejście „B” pMOS wygeneruje wysokie wyjście (1), a wejście „B” NMOS wygeneruje wyjście jako niskie (0). Tak więc ta bramka logiczna wygeneruje logiczną 1, ponieważ jest podłączona do źródła przez obwód zamknięty i odłączona od GND przez obwód otwarty.

Kiedy A to „1”, a B to „1”, wtedy wejście „pMOS” wygeneruje zero, a wejście nMOS wygeneruje „1”. W związku z tym powinniśmy również zweryfikować wejście B pMOS i nMOS. Wejście B pMOS wygeneruje „0”, a wejście B nMOS wygeneruje „1”. Tak więc ta bramka logiczna wygeneruje logiczne „0”, ponieważ jest odłączona od źródła przez obwód otwarty i jest połączona z GND przez obwód zamknięty.

Tabela prawdy

Tabela prawdy powyższego obwodu logicznego jest podana poniżej.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Napięcie progowe tranzystora PMOS to zwykle „Vgs”, które jest niezbędne do utworzenia kanału znanego jako inwersja kanału. W tranzystorze PMOS zaciski podłoża i źródła są po prostu podłączone do „Vdd”. Jeśli zaczniemy zmniejszać napięcie w odniesieniu do zacisku źródła na zacisku bramki od Vdd do punktu, w którym zauważysz inwersję kanału, w tej pozycji, jeśli przeanalizujesz Vgs i źródło będące na wysokim potencjale, otrzymasz wartość ujemną. Tak więc tranzystor PMOS ma ujemną wartość V.

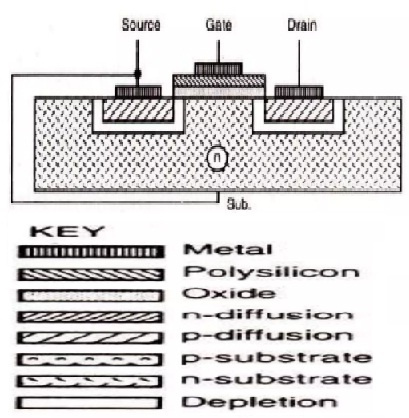

Proces wytwarzania PMOS

Kroki związane z wytwarzaniem tranzystorów PMOS omówiono poniżej.

Krok 1:

Cienka warstwa płytki krzemowej jest zmieniana w materiał typu N przez zwykłe domieszkowanie materiału fosforowego.

Krok 2:

Gruba warstwa dwutlenku krzemu (Sio2) jest hodowana na kompletnym podłożu typu p.

Krok 3:

Teraz powierzchnia jest pokryta fotorezystem na grubej warstwie dwutlenku krzemu.

Krok 4:

Następnie warstwa ta jest po prostu wystawiana na działanie światła UV przez maskę, która określa obszary, do których ma zachodzić dyfuzja wraz z kanałami tranzystorowymi.

Krok 5:

Obszary te są wytrawione wzajemnie z leżącym pod spodem dwutlenkiem krzemu, tak że powierzchnia płytki jest odsłonięta w oknie określonym przez maskę.

Krok 6:

Pozostała fotorezyst jest odłączana i cienka warstwa Sio2 jest zwykle hodowana na 0,1 mikrometra na całej powierzchni chipa. Następnie umieszcza się na nim polikrzem, aby utworzyć strukturę bramy. Fotorezyst jest umieszczony na całej warstwie polikrzemu i eksponuje światło UV przez maskę2.

Krok 7:

Dyfuzję uzyskuje się poprzez ogrzewanie płytki do maksymalnej temperatury i przepuszczanie gazu z pożądanymi zanieczyszczeniami typu p, takimi jak bor.

Krok 8:

Hoduje się dwutlenek krzemu o grubości 1 mikrometra i osadza się na nim materiał fotorezystu. Wyeksponuj światło ultrafioletowe z maską3 na preferowane obszary bramki, źródła i odpływu, które są wytrawione, aby wykonać nacięcia kontaktowe.

Krok 9:

Teraz metal lub aluminium osadza się na jego powierzchni o grubości 1 mikrometra. Ponownie materiał fotorezystu jest hodowany na całym metalu i eksponowany na światło UV przez maskę4, która jest wytrawiona w celu utworzenia wymaganego projektu połączenia. Ostateczna struktura PMOS jest pokazana poniżej.

Charakterystyka tranzystora PMOS

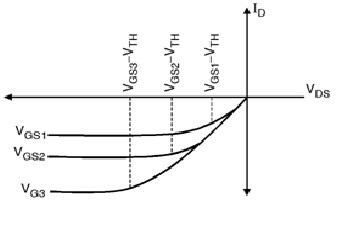

Charakterystykę I-V tranzystora PMOS przedstawiono poniżej. Charakterystyki te są podzielone na dwa obszary w celu uzyskania zależności między prądem drenu a źródłem (IDS), jak również jego napięciem końcowym, takim jak obszary liniowe i nasycenia.

W obszarze wkładki IDS będzie wzrastać liniowo, gdy VDS (napięcie drenu do źródła) wzrośnie, podczas gdy w obszarze nasycenia IDS jest stabilny i niezależny od VDS. Główny związek między ISD (prąd od źródła do drenu) a jego napięciami na zaciskach wynika z podobnej procedury tranzystora NMOS. W tym przypadku jedyną zmianą będzie to, że nośniki ładunku obecne w warstwie inwersyjnej to po prostu dziury. Kiedy otwory przemieszczają się od źródła do odpływu, przepływ prądu jest również taki sam.

Zatem znak ujemny pojawia się w bieżącym równaniu. Ponadto wszystkie zastosowane polaryzacje na zaciskach urządzenia są ujemne. Tak więc charakterystykę ID tranzystora PMOS – VDS przedstawiono poniżej.

Równanie prądu drenu dla tranzystora PMOS w obszarze liniowym ma postać:

ID = – mp Cox

Podobnie równanie prądu drenu dla tranzystora PMOS w obszarze nasycenia jest podane jako:

ID = – mp Cox (VSG – | V TH |p )^2

Gdzie „mp” to ruchliwość dziury, a „|VTH| p’ to napięcie progowe tranzystora PMOS.

W powyższym równaniu znak minus będzie wskazywał, że ID( prąd spustowy ) płynie od drenażu (D) do źródła (S), podczas gdy otwory płyną w przeciwnym kierunku. Kiedy ruchliwość dziury jest niska w porównaniu z ruchliwością elektronów, tranzystory PMOS cierpią z powodu możliwości napędu niskoprądowego.

Tak więc wszystko dotyczy przeglądu tranzystora PMOS lub tranzystora mos typu p - wytwarzania, obwodu i jego działania. PMOS zaprojektowano tranzystory z p-źródłem, n-substratem i drenem. Nośnikami ładunku PMOS są dziury. Tranzystor ten przewodzi po przyłożeniu niskiego napięcia do zacisku bramki. Urządzenia oparte na PMOS są mniej podatne na zakłócenia w porównaniu z urządzeniami NMOS. Tranzystory te mogą być stosowane jako rezystory sterowane napięciem, obciążenia czynne, zwierciadła prądowe, wzmacniacze transimpedancyjne, a także stosowane w przełącznikach i wzmacniaczach napięciowych. Oto pytanie do ciebie, co to jest tranzystor NMOS?