W poście omówiono funkcję pinoutów i inne ważne specyfikacje IC 4043. Dowiedzmy się o pełnym arkuszu danych tego bardzo interesującego układu.

Arkusz danych styków IC 4043

Technicznie IC 4043 jest zatrzaskiem czterostronnym ustawiania / resetowania (R / S) z 3 wyjściami stanów logicznych.

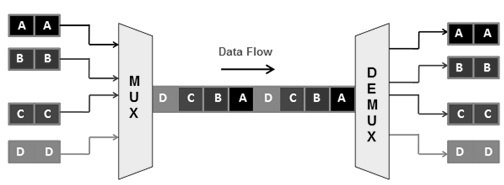

Mówiąc dokładniej, ten układ ma 4 zestawy wejść (czyli 8 pinów wejściowych) i 4 odpowiadające im pojedyncze wyjścia.

Te 4 zestawy wejść składają się z 4 par wejść ustawiania / resetowania.

Dla każdego ustawienia / resetu mamy jedno odpowiednie wyjście.

Wszystkie te ustawione wejścia resetowania odpowiadają na wysokie sygnały logiczne, tworząc efekt bistabilny na odpowiadających im pinach wyjściowych.

Bistabilny Flip / Flop

Bistabilny odnosi się do działania przerzutnika, innymi słowy, wysoki impuls na wejściu „ustawionym” powoduje, że odpowiednie wyjście jest wysokie z pierwotnego stanu niskiego, a stan wysoki do wejścia resetowania przywraca powyższy stan z wysokiego z powrotem do stanu niskiego.

Dlatego w zasadzie, aby odpowiednie wyjścia były wysokie, musimy zastosować wysoki na ich „ustawionych” wejściach, a aby ponownie ustawić wyjścia na niski, po prostu musimy zastosować kolejną wysoką wartość na ich wejściach resetujących.

Działanie pinów wejściowych i wyjściowych jest tak proste.

Oprócz tego układ scalony ma inny interesujący układ pinów wejściowych OE, który jest wspólnym układem pinów wyjściowych.

Funkcja ustawiania / resetowania

W celu umożliwienia opisanych powyżej działań ustawiania / resetowania w układzie scalonym, to wejście OE powinno być połączone z logicznym stanem wysokim lub po prostu z Vdd (głosowanie zasilania).

W powyższej sytuacji wyjście jest dozwolone z określonym działaniem przerzutnika.

Jeśli wejście OE jest połączone z masą, wyjście zawiesza się i wytwarza odpowiedź o wysokiej impedancji, czyli nie pokazuje ani niskiego wyjścia, ani wysokiego, raczej blokuje wejście w niereagujący stan zablokowany, stąd nazwa 3 stan logiczny wyjścia.

W ten sposób wejście OE może zostać użyte do wyłączenia działania układu scalonego, jeśli jest to wymagane dla określonej aplikacji.

Układ scalony działa najlepiej przy napięciach zasilania od 5 do 15 V.

Podsumujmy funkcje wyprowadzania wyjść wejściowych i specyfikacje IC 4043 z następującymi danymi:

- 1Q do 4Q (piny: 2, 9, 10, 1) 3-stanowe buforowane wyjście zatrzaskowe

- 1R do 4R (Piny: 3, 7, 11, 15) wejście resetowania (aktywne HIGH)

- 1S do 4S (Piny: 4, 6, 12, 14) ustawiane wejście (aktywne HIGH)

- OE (Pin: 5) wspólne wyjście włączające wejście

- VSS (Pin: 8) napięcie zasilania masy

- N.C. (Pin: 13) nie podłączony

- Napięcie zasilania VDD (styk: 16)

Więcej aktualizacji:

W tych postach staramy się zrozumieć działanie IC 4043 i IC 4044, studiując różne specyfikacje, arkusze danych urządzeń i ich rozmieszczenie.

Zasadniczo oba warianty to czterostanowe 3-stanowe R / S CMOS sprzężone krzyżowo lub zatrzaski resetowania / ustawiania. Quad oznacza posiadanie 4 wyjść, które mogą być ustawiane lub blokowane z logicznym stanem wysokim poprzez sterujący sygnał wejściowy lub resetowane do logicznego zera przez kolejny sygnał wejściowy.

Funkcja 3-stanowa umożliwia sterowanie układami scalonymi za pomocą 3 układów logicznych

Podstawowa zasada działania IC 4043 i IC 4044 jest taka sama jak powyżej, z tą różnicą, że IC 4043B są czterostanowymi sprzężonymi krzyżowo ANI Zatrzask i IC 4044B są czterostanowymi sprzężonymi krzyżowo NAND Zatrzask.

Schemat wyprowadzeń

Poniższe schematy wyprowadzeń układów scalonych pokazują wewnętrzną strukturę i szczegóły wyprowadzeń urządzeń:

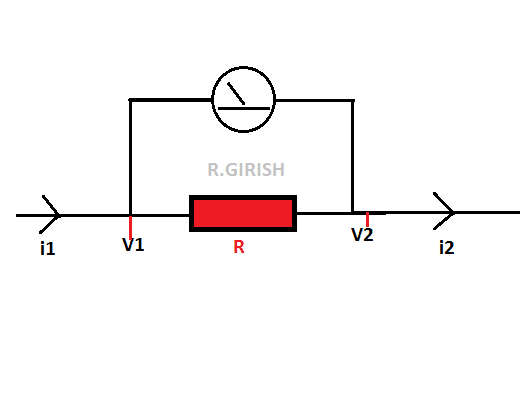

Na powyższych diagramach widzimy, że każdy z typów ma 4 zatrzaski z jednym wyjściem i 2 osobnymi wejściami RESET / SET. Funkcja styku ENABLE dla wszystkich wejść SET / RESET jest identyczna.

Wartość logiczna WYSOKA na pinie ENABLE umożliwia połączenie stanów zatrzasku z odpowiednimi wyjściami, wartość logiczna niska lub 0 odłącza stany zatrzasku od ich wyjść, powodując całkowite otwarcie obwodu na wyjściach.

NOR Latch, równoważne schematy logiczne zatrzasku NAND

Poniższe diagramy przedstawiają równoważne zatrzaski w postaci zatrzasków NOR i NAND, które znajdują się wewnątrz każdego z 4 zatrzasków poszczególnych układów scalonych.

Jak widać, każdy z bloków zatrzasków jest sterowany za pomocą 3 logicznych wejść sterujących, a mianowicie SET, RESET i ENABLE, dlatego wyjście jest zależne od tych 3 stanów wejściowych. Tabelę prawdy dla tych 3 stanów logicznych można poznać z poniższego diagramu:

W powyższej tabeli prawdy pełną formę różnych skróconych alfabetów symbolicznych można rozumieć w następujący sposób: S = SET Pin R = RESET Pin E = ENABLE Pin Q = OUTPUT Pin OC = Open Circuit NC = No Change

Główne cechy IC 4043 i IC 4044 są podsumowane poniżej:

Praktyczna podstawowa symulacja pracy pinów SET / RESET i ENABLE

Opis roboczy

Z powyższego GIF symulacji możemy zrozumieć działanie modułów poczwórnych zatrzasków z następującymi punktami:

Gdy styk SET jest podłączony z dodatnim zasilaniem, wyjście staje się wysokie i zostaje zablokowane, nawet jeśli dodatni potencjał zostanie usunięty z pinu SET, jak wskazuje czerwona dioda LED (przesunięcie w przód).

Gdy pin RESET jest przyłożony z dodatnim impulsem, zatrzask zostaje przerwany, a wyjście przechodzi w stan NISKI na stałe, nawet jeśli dodatni zostanie usunięty z kołka RESET. Jest to sygnalizowane świeceniem niebieskiej diody LED.

Powyższe operacje mogą być realizowane tylko wtedy, gdy pin ENABLE układu scalonego ma dodatni potencjał zasilania. Po podłączeniu do potencjału ujemnego lub uziemienia wyjście zatrzasku staje się otwarte i nie reaguje na operacje SET / RESET.

Poprzedni: Obwód programowalnego timera na dzień tygodnia Dalej: Wyprowadzenia IC 4033, arkusz danych, aplikacja