JTAG (Joint Test Action Group) to ugruntowany standard IEEE 1149.1, który został opracowany w roku 1980 w celu rozwiązania problemów produkcyjnych, które wystąpiły w płytach elektronicznych lub płytki z obwodami drukowanymi . Ta technologia służy do zapewnienia wystarczającego dostępu testowego dla każdej złożonej płyty, gdy dostęp testowy maleje. W ten sposób wprowadzono technologię skanowania granic i standard JTAG lub Specyfikacja JTAG jest ustalony. Złożoność elektroniki wzrasta z dnia na dzień, więc specyfikacja JTAG stała się akceptowanym formatem testowym do testowania skomplikowanych i kompaktowych jednostek elektronicznych. W tym artykule omówiono omówienie JTAG protokół – praca z aplikacjami.

Co to jest JTAG?

Nazwa nadana standardowemu testowemu portowi dostępowemu IEEE 1149.1 oraz architekturze Boundary-Scan jest znana jako JTAG (Joint Test Action Group). Ta architektura skanowania granic jest najczęściej używana w komputerze przetwórcy ponieważ pierwszy procesor z JTAG został wydany przez firmę Intel. Ten standard IEEE określa po prostu, w jaki sposób obwody komputera są testowane w celu potwierdzenia, czy działa on prawidłowo po zakończeniu procedury produkcyjnej. Na płytkach drukowanych przeprowadzane są testy sprawdzające połączenia lutowane.

Joint Test Action Group zapewnia widok wyprowadzeń dla testerów z każdym padem IC, co pomaga w identyfikacji wszelkich usterek na płytce drukowanej. Gdy ten protokół jest połączony z chipem, może on dołączyć sondę do chipa, umożliwiając programiście kontrolowanie chipa, a także jego połączeń z innymi chipami. Interfejs z grupą Joint Test Action może być również używany przez programistów do kopiowania oprogramowania układowego do pamięci nieulotnej w urządzeniu elektronicznym.

Konfiguracja/Wyjście

Wspólna Grupa Działań Testowych obejmuje 20 styków, gdzie każdy styk i jego funkcja są omówione poniżej.

Pin1 (VTref): Jest to pin napięcia odniesienia celu, który jest używany do podłączenia do głównego źródła zasilania celu, które waha się od 1,5 do 5,0 VDC.

Pin2 (Vzasilanie): Jest to docelowe napięcie zasilania, które jest używane do podłączenia głównego napięcia zasilania docelowego 1,5 VDC – 5,0 VDC.

Pin3 (nTRST): Jest to testowy pin resetowania, który służy do resetowania maszyny stanu kontrolera TAP.

Kołki (4, 6, 8, 10, 12, 14, 16, 18 i 20): Są to wspólne piny GND.

Pin5 (TDI): To są dane testowe w szpilce. Dane te są przenoszone do urządzenia docelowego. Ten pin musi być wyciągnięty w określonym stanie na tarczy docelowej.

Pin7 (TMS): To jest pin stanu trybu testowego, który jest wyciągany w celu określenia następnego stanu automatu stanu kontrolera TAP.

Pin9 (TCK): Jest to testowy pin zegarowy, który synchronizuje operacje wewnętrznego automatu stanu w sterowniku TAP.

Pin11 (RTCK): Jest to pin Input Return TCK używany w urządzeniach obsługujących taktowanie adaptacyjne.

Pin13 (TDO): To jest pin wyjścia danych testowych, więc dane są przenoszone z urządzenia docelowego do Flyswatter.

Pin15 (nSRST): Jest to pin resetowania systemu docelowego, który jest podłączony do głównego sygnału resetowania celu.

Piny 17 i 19 (NC): To nie są połączone piny.

Działa JTAG

Pierwotnym zastosowaniem JTAG jest testowanie graniczne. Oto prosta płytka drukowana zawierająca dwa układy scalone, takie jak procesor i FPGA . Typowa płyta może zawierać wiele układów scalonych. Ogólnie rzecz biorąc, układy scalone zawierają wiele pinów, które są połączone wspólnie z wieloma połączeniami. Tutaj, na poniższym schemacie, pokazane są tylko cztery połączenia.

Więc jeśli projektujesz wiele tablic, w których każda tablica ma tysiące połączeń. W tym są złe tablice. Musimy więc sprawdzić, która płytka działa, a która nie. W tym celu stworzono wspólną grupę działania testowego.

Ten protokół może wykorzystywać szpilki kontrolne wszystkich układów, ale na poniższym schemacie, Wspólna Grupa Działań Testowych wykona wszystkie szpilki wyjściowe procesora i wszystkie szpilki wejściowe FPGA. Następnie, przesyłając pewną ilość danych z pinów procesora i odczytując wartości pinów z FPGA, JTAG stwierdza, że połączenia płytki PCB są w porządku.

W rzeczywistości Wspólna Grupa Działań Testowych obejmuje cztery sygnały logiczne TDI, TDO, TMS i TCK. A te sygnały trzeba połączyć w określony sposób. Początkowo TMS i TCK są połączone równolegle ze wszystkimi układami scalonymi JTAG.

Następnie zarówno TDI, jak i TDO są połączone w celu utworzenia łańcucha. Jak widać, każdy układ scalony zgodny z JTAG zawiera 4 piny, które są używane dla JTAG, gdzie 3 piny są wejściami, a 4 pin jest wyjściem. Piąty pin, taki jak TRST, jest opcjonalny. Zwykle piny JTAG nie są współdzielone do innych celów.

Korzystając z Joint Test Action Group, wszystkie układy scalone wykorzystują testy graniczne, których pierwotny powód został stworzony przez JTAG. Obecnie użycie tego protokołu zostało rozszerzone, aby umożliwić różne rzeczy, takie jak konfiguracja FPGA, a następnie JTAG jest używany w rdzeniu FPGA do celów debugowania.

Architektura JTAG

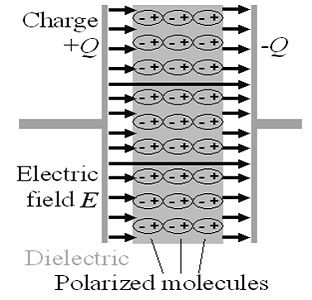

Poniżej przedstawiono architekturę JTAG. W tej architekturze wszystkie sygnały pomiędzy podstawową logiką urządzenia a pinami są przerywane przez szeregową ścieżkę skanowania zwaną BSR lub Boundary Scan Register. Ten BSR obejmuje różne „komórki” skanowania granicznego. Ogólnie rzecz biorąc, te komórki skanowania granicznego nie są widoczne, ale można ich użyć do ustawienia lub odczytu wartości w trybie testowym z pinów urządzenia.

Interfejs JTAG zwany TAP lub Test Access Port wykorzystuje różne sygnały do obsługi operacji skanowania granicznego, takie jak TCK, TMS, TDI, TDO i TRST.

- Sygnał TCK lub Test Clock po prostu synchronizuje wewnętrzne operacje automatu stanu.

- Sygnał TMS lub Test Mode Select jest próbkowany przy narastającym zboczu testowego sygnału zegarowego w celu określenia następnego stanu.

- Sygnał TDI lub Test Data In oznacza przesunięcie danych do urządzenia testowego, w przeciwnym razie logika programowania. Gdy wewnętrzna maszyna stanu jest w odpowiednim stanie, jest próbkowana na rosnącej krawędzi TCK.

- Sygnał TDO lub Test Data Out oznacza przesunięte dane urządzenia testowego, w przeciwnym razie logika programowania. Gdy wewnętrzna maszyna stanu jest we właściwym stanie, jest ważna na malejącej krawędzi TCK

- TRST lub Test Reset to opcjonalny pin, który jest używany do resetowania maszyny stanu kontrolera TAP.

Kontroler TAP

Testowy punkt dostępowy w architekturze JTAG składa się z kontrolera TAP, rejestru instrukcji i rejestrów danych testowych. Ten kontroler zawiera testującą maszynę stanu, która jest odpowiedzialna za odczyt sygnałów TMS i TCK. Tutaj pin danych i/p jest po prostu używany do ładowania danych do komórek granicznych między rdzeniem układu scalonego a fizycznymi pinami, a także do ładowania danych do jednego z rejestrów danych lub do rejestru instrukcji. Pin danych o/p służy do odczytu danych z rejestrów lub komórek granicznych.

Maszyna stanów kontrolera TAP jest kontrolowana przez TMS i jest taktowana przez TCK. Maszyna stanów używa dwóch ścieżek do oznaczania dwóch różnych trybów, takich jak tryb instrukcji i tryb danych.

Rejestry

W ramach skanowania granic dostępne są dwa rodzaje rejestrów. Każde zgodne urządzenie zawiera minimum dwa lub więcej rejestrów danych i jeden rejestr instrukcji.

Rejestr instrukcji

Rejestr instrukcji służy do przechowywania bieżącej instrukcji. Tak więc jego dane są wykorzystywane przez kontroler TAP do decydowania, co wykonać z otrzymanymi sygnałami. Najczęściej dane z rejestru rozkazów opisują, do którego z rejestrów danych należy przekazać sygnały.

Rejestry danych

Rejestry danych są dostępne w trzech typach: rejestr BSR (Boundary Scan Register), rejestr BYPASS i KODY ID. Mogą tam również znajdować się inne rejestry danych, jednak nie są one konieczne jako element standardu JTAG.

Rejestr skanowania granic (BSR)

BSR jest głównym rejestrem danych testowych, który służy do przenoszenia danych zi do pinów I/O urządzenia.

OBJAZD

Bypass to jednobitowy rejestr służący do przekazywania danych z TDI – TDO. Dzięki temu dodatkowe urządzenia w obwodzie mogą być testowane przy minimalnym nakładzie pracy.

KODY ID

Ten typ rejestru danych zawiera kod ID oraz numer wersji urządzenia. Tak więc dane te umożliwiają podłączenie urządzenia do jego pliku BSDL (Boundary Scan Description Language). Ten plik zawierał szczegóły konfiguracji Boundary Scan dla urządzenia.

Działanie JTAG jest początkowo wybierane w trybie instrukcji, w którym jeden ze stanów w tym trybie „ścieżka” pozwala zegarowi operatora w ramach instrukcji TDI. Następnie machina państwowa rozwija się, aż się przestawia. Następnym krokiem w przypadku większości instrukcji jest wybór trybu danych. Tak więc w tym trybie dane są ładowane przez TDI w celu odczytania z TDO. W przypadku TDI i TDO, ścieżki danych zostaną ustawione zgodnie z instrukcją, która została taktowana. Po zakończeniu operacji odczytu/zapisu, ponownie maszyna stanu przechodzi w stan resetowania.

Różnica między JTAG a UART

Różnica między JTAG i UART obejmuje następujące elementy.

| JTAG |

UART |

| Termin „JTAG” oznacza Joint Test Action Group. | Termin ' UART ” oznacza uniwersalny asynchroniczny odbiornik/nadajnik. |

| Jest to synchroniczny interfejs, który wykorzystuje wbudowany sprzęt do programowania lampy błyskowej . | UART to asynchroniczny interfejs, który wykorzystuje bootloader działający w pamięci. |

| Jest to zestaw portów testowych, które służą do debugowania, ale mogą być również używane do programowania oprogramowania układowego (co jest powszechnie wykonywane).

|

UART to rodzaj układu sterującego komunikacją do i z urządzenia, takiego jak mikrokontroler, ROM, RAM itp. W większości przypadków jest to połączenie szeregowe, które pozwala nam komunikować się z urządzeniem. |

| Są one dostępne w czterech typach TDI, TDO, TCK, TMS i TRST. | Są one dostępne w dwóch typach głupich UART i FIFO UART. |

| Joint Test Action Group to programowanie szeregowe lub protokół dostępu do danych, który jest używany do łączenia mikrokontrolerów i powiązanych urządzeń. | UART jest jednym z rodzajów chipów, inaczej podkomponentem mikrokontrolera, który służy do dostarczania sprzętu do generowania asynchronicznego strumienia szeregowego, takiego jak RS-232/RS-485. |

| Komponenty JTAG to procesory, układy FPGA, CPLD itp. | Komponenty UART to generator CLK, rejestry przesuwne we/wy, bufory nadawcze lub odbiorcze, bufor magistrali danych systemowych, logika sterowania odczytem lub zapisem itp. |

Analizator protokołu JTAG

JTAG Protocol Analyzer, taki jak PGY-JTAG-EX-PD, jest jednym z rodzajów analizatora protokołów, zawierającym pewne funkcje do przechwytywania i debugowania komunikacji między testowanym hostem a projektem. Ten typ analizatora jest wiodącym instrumentem, który pozwala inżynierom testującym i projektowym na testowanie poszczególnych projektów JTAG pod kątem ich specyfikacji poprzez aranżowanie PGY-JTAG-EX-PD jak Master lub Slave w celu generowania ruchu JTAG i dekodowania pakietów dekodowania Protokół Wspólnej Grupy Działania Testu.

Cechy

Funkcje analizatora protokołu JTAG obejmują następujące elementy.

- Obsługuje do 25MH częstotliwości JTAG.

- Generuje jednocześnie ruch JTAG i dekodowanie protokołu dla magistrali.

- Posiada funkcję JTAG Master.

- Zmienne prędkości danych JTAG i cykl pracy.

- Zdefiniowane przez użytkownika opóźnienia TDI i TCK.

- Interfejs USB 2.0 lub 3.0 komputera hosta.

- Analiza błędów w ramach dekodowania protokołu

- Schemat taktowania magistrali dekodowanej protokołem.

- Ciągłe przesyłanie strumieniowe danych protokołu do komputera hosta w celu zapewnienia dużego bufora.

- Lista aktywności protokołu.

- Przy różnych prędkościach można napisać skrypt ćwiczeń, aby połączyć generowanie wielu ramek danych.

Schemat czasowy

The schemat rozrządu JTAG Protokół pokazano poniżej. Na poniższym schemacie pin TDO pozostaje w stanie wysokiej impedancji, z wyjątkiem stanu kontrolera shift-IR/shift-DR.

W warunkach kontrolera shift-IR i Shift-DR, pin TDO jest aktualizowany na malejącej krawędzi TCK przez Target i próbkowany na rosnącej krawędzi TCK przez Host.

Oba piny TDI i TMS są po prostu próbkowane na rosnącej krawędzi TCK przez Target. Zaktualizowano na opadającej krawędzi, w przeciwnym razie TCK przez hosta.

Aplikacje

The Aplikacje JTAG obejmują następujące elementy.

- Joint Test Action Group jest często wykorzystywana w procesorach w celu zapewnienia prawa dostępu do ich funkcji emulacji lub debugowania.

- Wszystkie CPLD i FPGA używają tego jako interfejsu dającego dostęp do swoich funkcji programistycznych.

- Służy do testowania płytek drukowanych bez fizycznego dostępu

- Służy do testów produkcyjnych na poziomie płyty.

Tak więc o to chodzi przegląd JTAG – konfiguracja pinów, praca z aplikacjami. Standard przemysłowy JTAG jest używany do weryfikacji projektu, a także testowania PCB po produkcji. Oto pytanie do Ciebie, JTAG oznacza?

![Diody stykowe punktowe [historia, konstrukcja, obwód aplikacyjny]](https://electronics.jf-parede.pt/img/electronics-tutorial/38/point-contact-diodes-history-construction-application-circuit-1.jpg)