W tym poście dowiemy się, jak budować bramki logiczne NOT, AND, NAND, OR i NOR przy użyciu tranzystorów dyskretnych. Główną zaletą stosowania tranzystorowych bramek logicznych jest to, że mogą pracować nawet z napięciami tak niskimi, jak 1,5 V.

W niektórych aplikacjach elektronicznych dostępne napięcie może być niewystarczające do zasilania układów scalonych TTL lub nawet CMOS. Dotyczy to zwłaszcza gadżetów zasilanych bateriami. Bez wątpienia zawsze masz opcję 3-woltowego układu logicznego. Jednak nie zawsze są one łatwo dostępne dla entuzjastów lub eksperymentatorów i nie działają poniżej określonych specyfikacji napięcia (zwykle poniżej 2,5 wolta prądu stałego).

Co więcej, w aplikacji zasilanej bateryjnie może być miejsce tylko na pojedynczą baterię 1,5 V. Więc co zamierzasz zrobić? Zwykle Bramki logiczne IC można zastąpić tranzystorowymi bramkami logicznymi. Dla każdej konkretnej bramki logicznej zwykle wymagane jest tylko kilka tranzystorów, a dla typowej logiki falownika z bramką NOT wymagany jest tylko jeden tranzystor.

FET kontra tranzystor bipolarny

Tranzystory polowe (FET) vs tranzystory bipolarne : która opcja jest lepsza dla niskonapięciowych obwodów logicznych? Jedna wspaniała cecha FAKTY jest to, że ich opór „włączenia” jest niewiarygodnie niski. Dodatkowo potrzebują bardzo niskiego prądu załączającego bramkę.

Mają jednak jedno ograniczenie w zastosowaniach ekstremalnie niskonapięciowych. Zazwyczaj limit napięcia bramki wynosi około jednego wolta. Ponadto dostępne napięcie może spaść poniżej optymalnego zakresu roboczego FET, jeśli do bramki podłączony jest rezystor ograniczający prąd lub obniżający napięcie.

I odwrotnie, bipolarne tranzystory przełączające mają przewagę w zastosowaniach z pojedynczą baterią o ekstremalnie niskim napięciu, ponieważ do włączenia potrzebują tylko 0,6 do 0,7 wolta.

Co więcej, większość popularnych tranzystorów FET, które są zwykle sprzedawane w opakowaniach bąbelkowych w najbliższym sklepie elektronicznym, jest często droższa niż tranzystory bipolarne. Ponadto hurtowy pakiet tranzystorów bipolarnych można ogólnie kupić za cenę pary FET.

Obsługa FET wymaga znacznie większej uwagi niż obsługa tranzystorów bipolarnych. Nadużycia elektrostatyczne i ogólne eksperymentalne sprawiają, że FET są szczególnie podatne na uszkodzenia. Spalone komponenty mogą zrujnować przyjemny, kreatywny wieczór pełen eksperymentów lub innowacji, nie zapominając o emocjonalnym bólu związanym z debugowaniem.

Podstawy przełączania tranzystorów

Przykłady obwodów logicznych wyjaśnione w tym artykule wykorzystują bipolarne tranzystory NPN, ponieważ są one niedrogie i nie wymagają specjalnej obsługi. Aby uniknąć uszkodzenia urządzenia lub części, które je podtrzymują, przed podłączeniem obwodu należy podjąć odpowiednie środki bezpieczeństwa.

Mimo że nasze obwody są głównie skoncentrowane na tranzystorach bipolarnych (BJT), równie dobrze mogłyby być skonstruowane przy użyciu technologii FET.

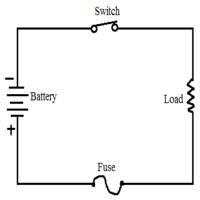

Podstawowy obwód przełącznika to prosta aplikacja tranzystorowa, która jest jedną z najłatwiejszych konstrukcji.

Tworzenie bramki NOT z pojedynczym tranzystorem

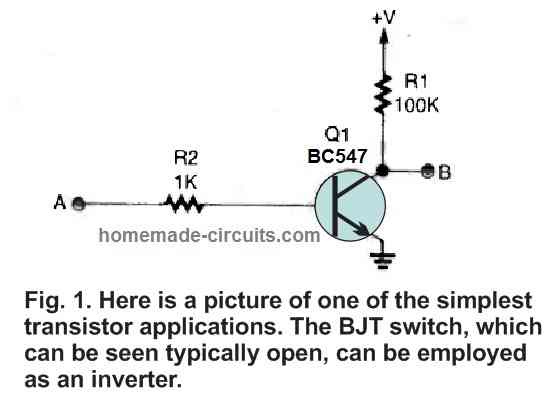

Schemat przełącznika tranzystorowego pokazano na rysunku 1. W zależności od tego, jak jest zaimplementowany w konkretnej aplikacji, przełącznik może być postrzegany jako utrzymywany w stanie niskim lub normalnie otwarty.

Prostą bramkę logiczną falownika typu NOT można utworzyć za pomocą prostego obwodu przełączającego pokazanego na rys. 1 (gdzie punkt A jest wejściem). Bramka NOT działa w taki sposób, że jeśli do bazy tranzystora (punkt A; Q1) nie zostanie doprowadzona żadna polaryzacja DC, to pozostanie ona odcięta, co skutkuje wysokim lub logicznym 1 (równym poziomowi V+) na wyjściu ( punkt B).

Tranzystor jednak aktywuje się, gdy do bazy Q1 zostanie doprowadzona odpowiednia polaryzacja, spychając wyjście układu w stan niski lub do logicznego 0 (prawie równego zerowemu potencjale). Tranzystor oznaczony jako Q1 jest tranzystorem bipolarnym ogólnego przeznaczenia lub BC547, który jest zwykle używany w aplikacjach przełączania i wzmacniaczy o małej mocy.

Każdy tranzystor, który jest mu równoważny (np. 2N2222, 2N4401, itd.) będzie działał. Wartości R1 i R2 zostały wybrane tak, aby znaleźć kompromis między niskim poborem prądu a kompatybilnością. We wszystkich projektach wszystkie rezystory są 1/4 watowe, 5% jednostek.

Napięcie zasilania jest regulowane w zakresie od 1,4 do 6 V DC. Zauważ, że obwód może działać jak bufor, gdy rezystor obciążenia i połączenie wyjściowe są przesunięte na emiter tranzystora.

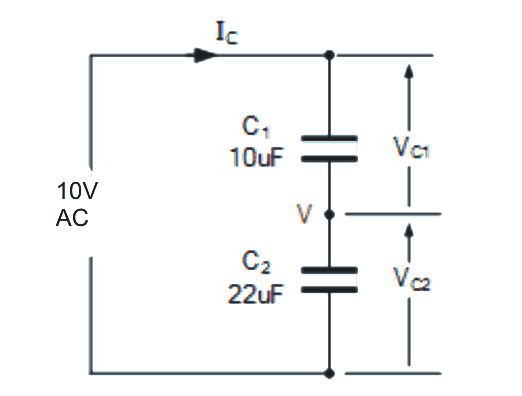

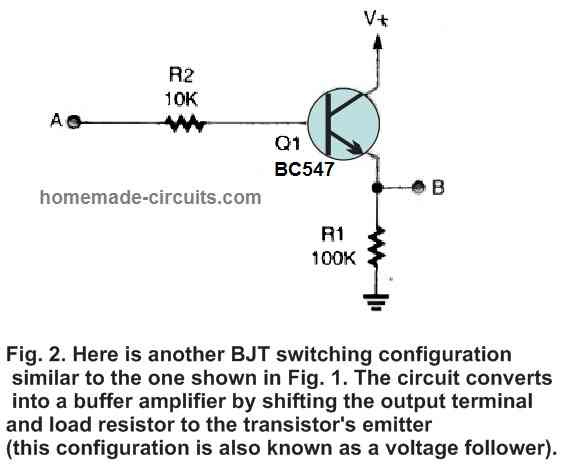

Wykonanie bramki buforowej za pomocą pojedynczego BC547 BJT

Wtórnik napięciowy, czyli wzmacniacz buforowy, jest typem logicznej konfiguracji przełączania identycznej do pokazanej na rysunku 2. Należy zauważyć, że rezystor obciążenia i zacisk wyjściowy zostały w tym obwodzie przesunięte z kolektora tranzystora na jego emiter, co jest podstawowa różnica między tą konstrukcją a tą pokazaną na ryc. 1.

Działanie tranzystora można również „odwrócić” poprzez przeniesienie rezystora obciążenia i zacisku wyjściowego na drugi koniec BJT.

Innymi słowy, gdy nie ma polaryzacji na wejściu obwodu, wyjście obwodu pozostaje niskie; jednak, gdy do wejścia obwodu zostanie doprowadzona polaryzacja o odpowiednim napięciu, wyjście obwodu staje się wysokie. (Jest to dokładnie odwrotność tego, co dzieje się we wcześniejszym obwodzie.)

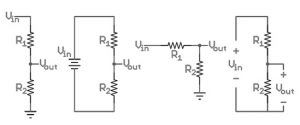

Projektowanie dwuwejściowych bramek logicznych z wykorzystaniem tranzystorów

AND Brama wykorzystująca dwa tranzystory

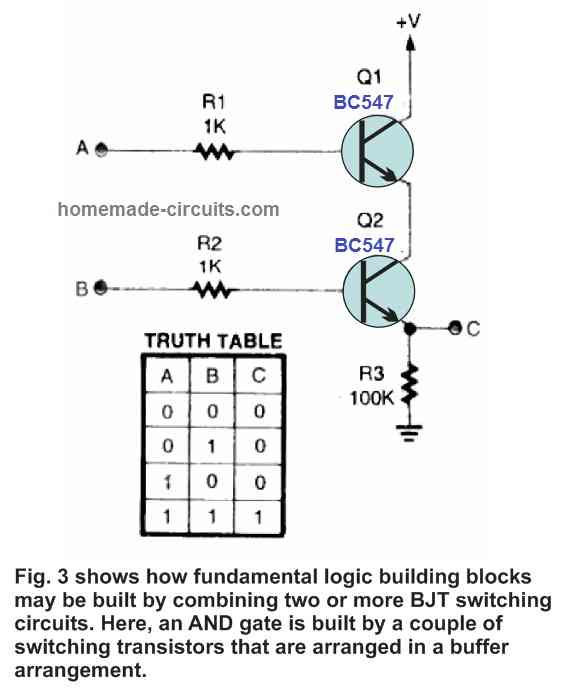

Rysunek 3 ilustruje, w jaki sposób można utworzyć podstawową dwuwejściową bramkę AND przy użyciu pary buforów wraz z tabelą prawdy dla tej bramki. Tabela prawdy ilustruje, jakie byłyby wyniki wyjściowe dla każdego odrębnego zestawu danych wejściowych. Punkty A i B służą jako wejścia układu, a punkt C służy jako wyjście układu.

Ważne jest, aby z tabeli prawdy zauważyć, że tylko jeden zestaw parametrów wejściowych daje sygnał wyjściowy o wysokiej wartości logicznej, podczas gdy wszystkie inne kombinacje wejściowe dają sygnał wyjściowy o niskiej wartości logicznej. Wyjście bramki AND na rysunku 3 pozostaje nieco poniżej V+, gdy osiągnie wysoki poziom.

Dzieje się tak z powodu spadku napięcia między dwoma tranzystorami (Q1 i Q2).

Bramka NAND wykorzystująca dwa tranzystory

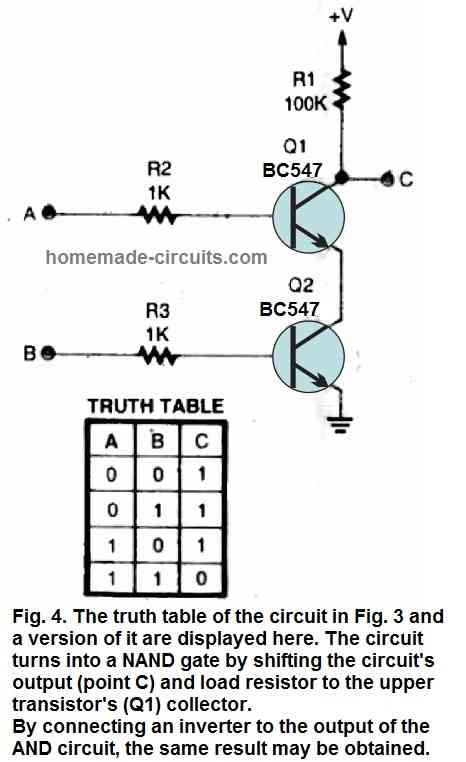

Inny wariant obwodu z rysunku 3 i powiązaną tabelę prawdy pokazano na rysunku 4. Obwód zamienia się w bramkę NAND poprzez przesunięcie wyjścia (punkt C) i rezystora wyjściowego do górnego kolektora tranzystora (Q1).

Ponieważ oba Q1 i Q2 muszą być włączone, aby pociągnąć niską stronę R1 do masy, spadek napięcia na wyjściu C jest nieznaczny.

Jeśli tranzystorowe AND lub tranzystorowe bramki NAND wymagają więcej niż dwóch wejść, w przedstawionych projektach można połączyć więcej tranzystorów, aby zapewnić trzy, cztery itd. wejściowe bramki AND lub NAND.

Aby jednak skompensować straty napięcia poszczególnych tranzystorów, należy odpowiednio zwiększyć V+.

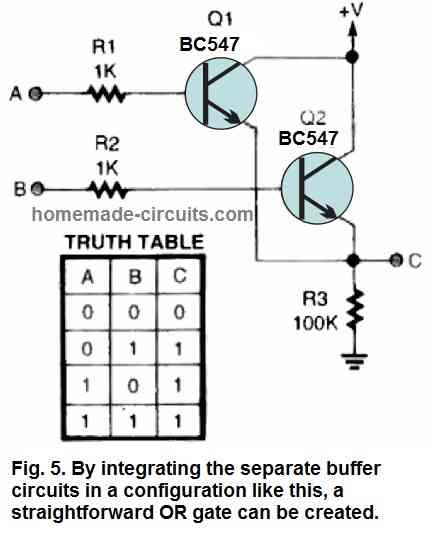

Brama LUB wykorzystująca dwa tranzystory

Inną formę obwodu logicznego z dwoma wejściami można zobaczyć na rysunku 5, wraz z tabelą prawdy obwodu bramki OR.

Wyjście obwodu jest wysokie, gdy albo wejście A, albo wejście B jest w stanie wysokim, jednak ze względu na kaskadowe tranzystory spadek napięcia przekracza 0,5 wolta. Po raz kolejny wyświetlone liczby wskazują, że napięcie i prąd są wystarczające do obsługi kolejnej bramki tranzystorowej.

Brama NOR wykorzystująca dwa tranzystory

Rysunek 6 przedstawia kolejną bramkę na naszej liście, dwuwejściową bramkę NOR, wraz z jej tabelą prawdy. Podobnie jak bramki AND i NAND reagują na siebie, obwody OR i NOR robią to samo.

Każda z wyświetlonych bramek jest w stanie dostarczyć wystarczającą ilość napędu, aby aktywować co najmniej jedną lub więcej sąsiednich bramek tranzystorowych.

Zastosowania tranzystorowej bramki logicznej

Co robisz z opisanymi powyżej obwodami cyfrowymi, które teraz posiadasz? Wszystko, co można osiągnąć za pomocą konwencjonalnych bramek TTL lub CMOS, ale bez obaw o ograniczenia napięcia zasilania. Oto kilka zastosowań bramek tranzystorowych w działaniu.

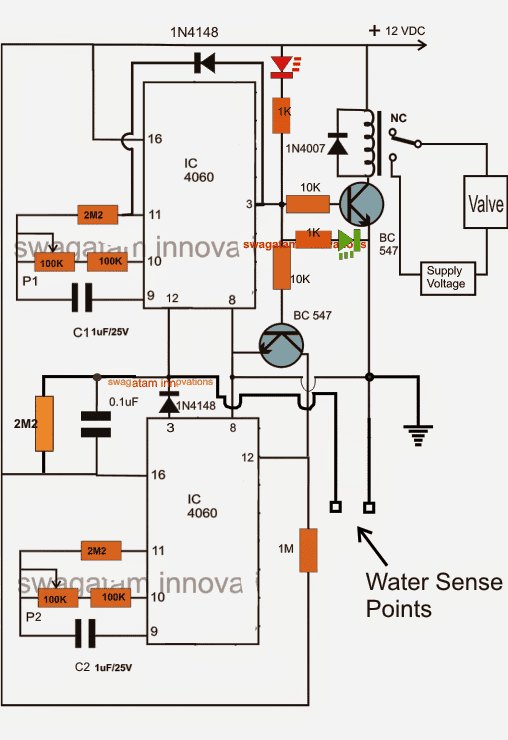

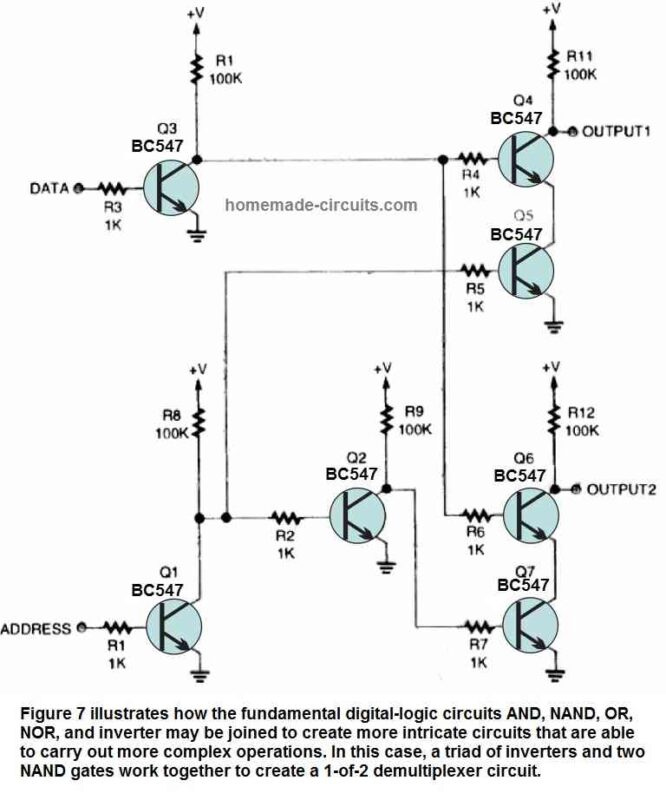

Obwód demultipleksera

Demultiplekser 1 z 2 z trzema bramkami NOT i dwoma obwodami NAND jest pokazany na rysunku 7. Odpowiednie wyjście jest wybierane za pomocą jednobitowego „wejścia adresowego”, którym może być albo OUTPUT1 albo OUTPUT2, podczas gdy podawane są informacje sterujące. do obwodu za pomocą wejścia DATA.

Obwód działa najskuteczniej, gdy szybkość transmisji danych jest utrzymywana poniżej 10 kHz. Funkcjonalność obwodu jest prosta. Wejście DATA jest dostarczane z wymaganym sygnałem, który włącza Q3 i odwraca dane przychodzące do kolektora Q3.

Wyjście Q1 jest ustawiane w stan wysoki, jeśli wejście ADDRESS jest w stanie niskim (uziemienie lub brak sygnału). W kolektorze Q1 wysoka moc dzielona jest na dwie ścieżki. W pierwszej ścieżce wyjście Q1 jest dostarczane do bazy Q5 (jednej z dwuwejściowych odnóg bramki NAND), włączając ją i tym samym „aktywując” bramkę NAND złożoną z Q4 i Q5.

W drugiej ścieżce wysokie wyjście Q1 jest jednocześnie podawane na wejście innej bramki NOT (Q2). Po przejściu podwójnej inwersji, wyjście Q2 spada. Ten niski jest zasilany przez bazę Q7 (jeden zacisk drugiej bramki NAND, zbudowanej z Q6 i Q7), wyłączając w ten sposób obwód NAND.

W takich okolicznościach każda informacja lub sygnał doprowadzony do wejścia DATA dociera do OUTPUT1. Alternatywnie sytuacja jest odwrotna, jeśli na wejście ADDRESS podawany jest wysoki sygnał. Oznacza to, że wszelkie informacje dostarczone do obwodu będą wyświetlane na WYJŚCIU 2, ponieważ bramka NAND Q4/Q5 jest wyłączona, a bramka NAND Q6/Q7 jest włączona.

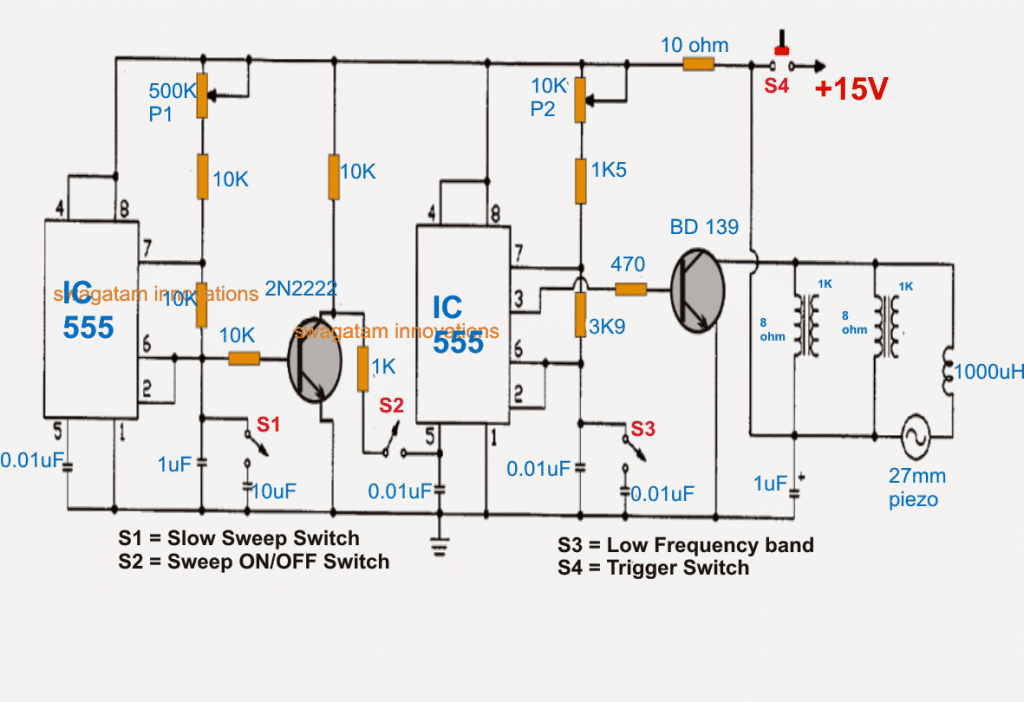

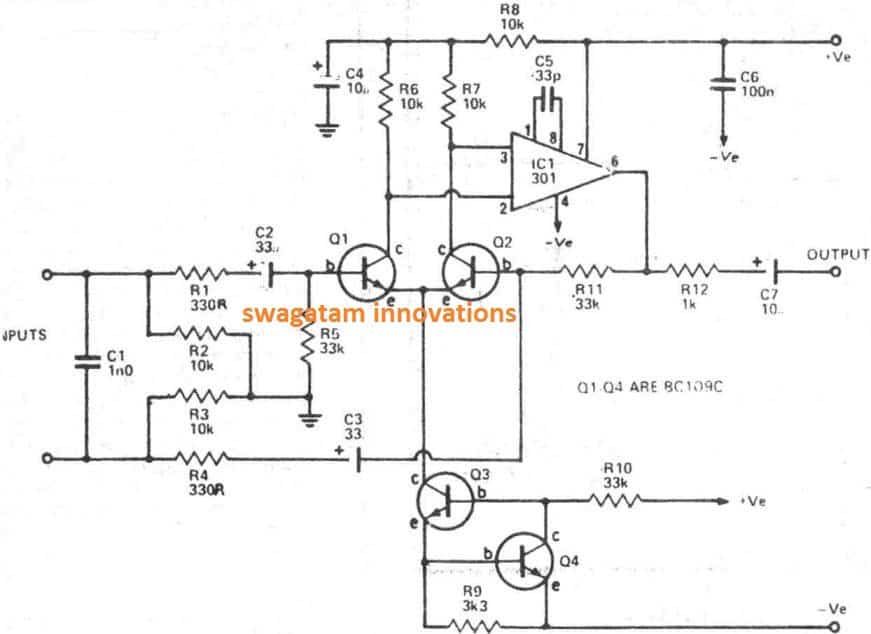

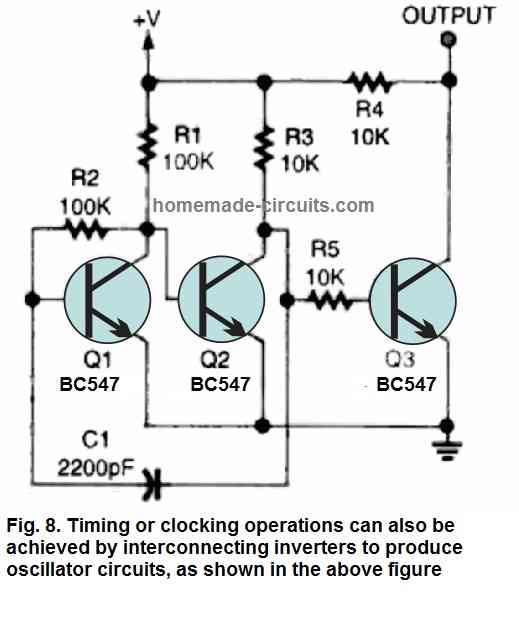

Obwód oscylatora (generator zegara)

Nasza następna aplikacja tranzystorowej bramki logicznej, zilustrowana na rys. 8, to podstawowy generator zegara (znany również jako oscylator) złożony z trzech zwykłych falowników bramki NOT (z których jeden jest spolaryzowany za pomocą rezystora sprzężenia zwrotnego, R2, który umieszcza go w region analogowy).

Aby wyrównać wyjście, dołączona jest trzecia bramka NOT (Q3), która dostarcza uzupełnienie do wyjścia oscylatora. Wartość C1 można zwiększać lub zmniejszać, aby zmienić częstotliwość roboczą obwodu. Przebieg wyjściowy ma częstotliwość około 7 kHz z V+ przy 1,5 V DC, przy użyciu wskazanych wartości składowych.

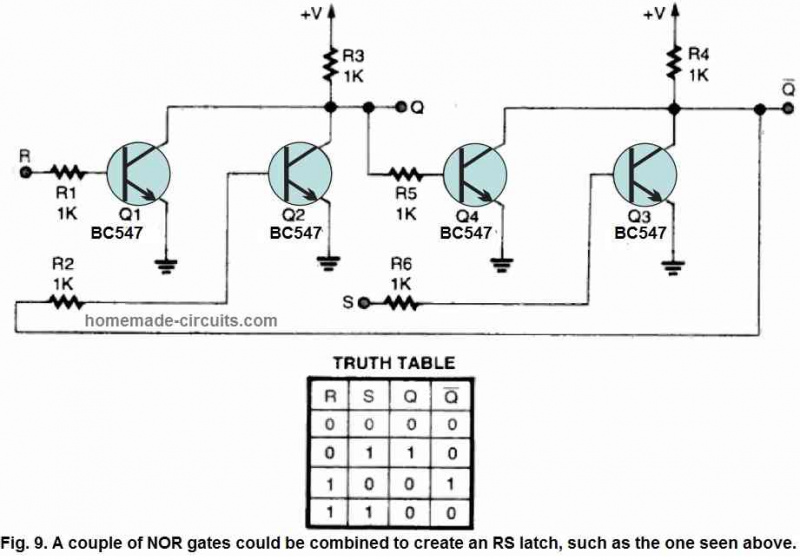

Obwód zatrzasku RS

Rys. 9 pokazuje nasz ostateczny obwód aplikacyjny, zatrzask RS złożony z dwóch bramek NOR. Aby zapewnić prawidłowe wysterowanie wyjścia na wyjściach Q i Q, rezystory R3 i R4 są ustawione na 1 kΩ.

Tabela prawdy zatrzasku RS jest wyświetlana obok schematu. To tylko kilka ilustracji kilku wiarygodnych, niskonapięciowych, cyfrowych obwodów z bramką logiczną, które można stworzyć przy użyciu pojedynczych tranzystorów.

Obwody wykorzystujące logikę tranzystorową wymagają zbyt wielu części

Wiele problemów można rozwiązać za pomocą wszystkich tych tranzystorowych obwodów logicznych niskiego napięcia. Jednak zastosowanie zbyt wielu tych tranzystorowych bramek może prowadzić do nowych problemów.

Liczba tranzystorów i rezystorów może być dość duża, jeśli budowana aplikacja zawiera dużą liczbę bramek, zajmujących cenną przestrzeń.

Jednym ze sposobów rozwiązania tego problemu jest zastosowanie tablic tranzystorowych (wiele tranzystorów zamkniętych w plastiku) i rezystorów SIP (Single Inline Package) w miejsce pojedynczych jednostek.

Powyższe podejście pozwala zaoszczędzić tonę miejsca na płytce drukowanej przy zachowaniu wydajności równej ich pełnowymiarowym odpowiednikom. Macierze tranzystorowe są oferowane w opakowaniach do montażu powierzchniowego, 14-stykowych otworów przelotowych i poczwórnych.

W przypadku większości obwodów mieszanie typów tranzystorów może być całkiem do przyjęcia.

Niemniej jednak wskazane jest, aby eksperymentator pracował z jednym typem tranzystora do budowy tranzystorowych obwodów logicznych (co oznacza, że jeśli utworzysz sekcję bramki za pomocą BC547, spróbuj użyć tego samego BJT do wykonania pozostałych bramek).

Rozumowanie jest takie, że różne warianty tranzystorów mogą mieć nieco inne właściwości, a zatem mogą zachowywać się inaczej.

Na przykład, w przypadku niektórych tranzystorów granica włączenia bazy może być większa lub mniejsza niż inna, lub też ogólny zysk prądu może być nieco wyższy lub niższy.

Z drugiej strony koszt zakupu opakowania zbiorczego jednego typu tranzystora może być również niższy. Wydajność twoich obwodów poprawi się, jeśli twoje bramki logiczne zostaną zbudowane przy użyciu dopasowanych tranzystorów, a cały projekt będzie ostatecznie bardziej satysfakcjonujący.