Na co dzień spotykamy się z różnego rodzaju gadżetami elektronicznymi. Jedną z technologii, która wywołała rewolucję w produkcji elektroniki, jest „ Układ scalony „. Ta technologia zmniejszyła rozmiar produktów elektronicznych poprzez zwiększenie gęstości bramki logiczne za chip. Obecnie mamy różne typy i konfiguracje układów scalonych. Jak obserwujemy wokół, odkrywamy, że niektóre układy scalone mogą być używane tylko do jednej określonej aplikacji, podczas gdy niektóre układy scalone można przeprogramować i używać do różnych aplikacji. Te typy układów scalonych noszą nazwę ASIC. Ale czym się różnią? Jak można je przeprogramować? Dlaczego niektórych układów scalonych nie można przeprogramować? Przejdź dalej, aby znaleźć odpowiedzi na te pytania.

Co to jest ASIC (układ scalony specyficzny dla aplikacji)?

Pełna forma ASIC to Układ scalony specyficzny dla aplikacji. Te obwody są specyficzne dla aplikacji, tj. dostosowane układy scalone dostosowane do określonej aplikacji. Są one zwykle projektowane od poziomu głównego na podstawie wymagań konkretnej aplikacji. Niektóre z podstawowych przykłady układów scalonych specyficznych dla aplikacji są chipami używanymi w zabawkach, chipem używanym do łączenia pamięci i mikroprocesora itp. Te chipy mogą być używane tylko do tej jednej aplikacji, dla której zostały zaprojektowane. Przypuszczalnie te rodzaje układów scalonych są preferowane tylko dla tych produktów, które mają dużą serię produkcyjną. Ponieważ układy ASIC są projektowane od poziomu głównego, mają wysoki koszt i są zalecane tylko do produkcji na dużą skalę.

Główną zaletą ASIC jest zmniejszony rozmiar chipa, ponieważ duża liczba funkcjonalnych jednostek obwodu jest zbudowana na jednym chipie. Nowoczesne ASIC zazwyczaj zawiera 32-bitowy mikroprocesor , bloki pamięci, obwody sieciowe itp… Taki typ układów ASIC jest znany jako System na chipie . Wraz z rozwojem technologii produkcji i zwiększonymi badaniami w zakresie metod projektowania opracowywane są układy ASIC o różnych poziomach dostosowania.

Rodzaje ASIC

Układy ASIC są podzielone na kategorie w oparciu o stopień dostosowania, jakie programista może wykonać na chipie.

Rodzaje układów ASIC

Pełne niestandardowe

W tego typu konstrukcji wszystkie komórki logiczne są dostosowane do konkretnych zastosowań, tj. projektant musi specjalnie wykonać komórki logiczne dla obwodów. Wszystkie warstwy masek do połączeń są dostosowywane. Dlatego programista nie może zmienić połączeń układu scalonego i podczas programowania musi być świadomy układu obwodu.

Jednym z najlepszych przykładów Full custom ASIC jest mikroprocesor. Ten rodzaj dostosowywania umożliwia projektantom budowanie różnych obwodów analogowych, zoptymalizowanych komórek pamięci lub struktur mechanicznych na jednym układzie scalonym. Ten układ ASIC jest kosztowny i bardzo czasochłonny w produkcji i projektowaniu. Zaprojektowanie tych układów scalonych zajmuje około ośmiu tygodni.

Są one zwykle przeznaczone do aplikacji wysokiego poziomu. Maksymalna wydajność, zminimalizowany obszar i najwyższy stopień elastyczności to główne cechy pełnego niestandardowego projektu. Ostatecznie ryzyko jest duże podczas projektowania, ponieważ komórki logiczne, rezystory itp.… Stosowane elementy obwodów nie są wstępnie testowane.

Pół-niestandardowe

W tego typu projektach komórki logiczne są pobierane z bibliotek standardowych, tj. nie są wykonane ręcznie, jak w pełnym niestandardowym projekcie. Niektóre maski są dostosowywane, a inne są pobierane z wstępnie zaprojektowanej biblioteki. W oparciu o typ komórek logicznych pobranych z biblioteki i ilość dostosowań dozwolonych dla połączeń międzysieciowych, te układy ASIC są podzielone na dwa typy - ASIC oparty na standardowej komórce i ASIC oparty na macierzy bramkowej.

1). Standardowy układ ASIC oparty na ogniwie

Aby poznać te IC, najpierw zrozumiemy, co oznacza standardowa biblioteka komórek. Niektóre komórki logiczne, takie jak Bramki AND, bramki OR multipleksery, japonki są wstępnie zaprojektowane przez projektantów przy użyciu różnych konfiguracji, ustandaryzowane i zapisane w postaci biblioteki. Ta kolekcja jest znana jako standardowa biblioteka komórek.

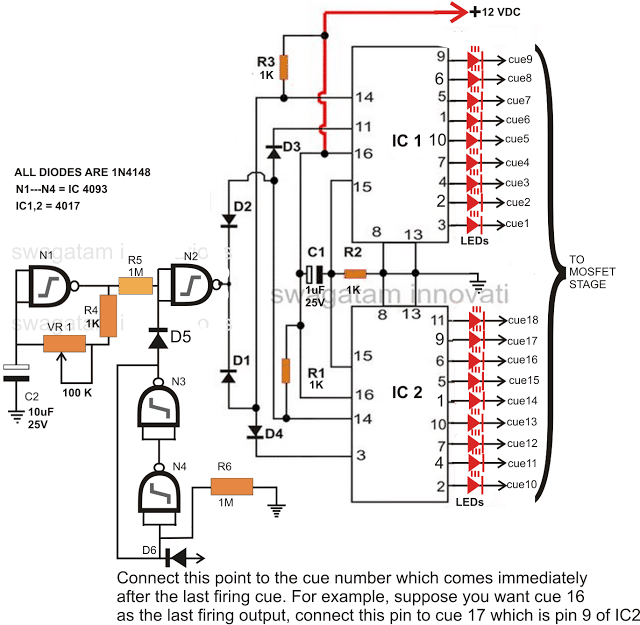

Standardowy układ ASIC oparty na ogniwach

W standardowych komórkach używane są komórki logiczne ASIC z tych standardowych bibliotek. Na chipie ASIC standardowy obszar komórek lub elastyczny blok składa się ze standardowych komórek ułożonych w rzędy. Wraz z tymi elastycznymi blokami na chipie stosowane są megakomórki, takie jak mikrokontrolery, a nawet mikroprocesory. Te mega komórki są również znane jako Mega-funkcje, makra na poziomie systemu, stałe bloki, funkcjonalne standardowe bloki.

Powyższy rysunek przedstawia standardową komorę ASIC z pojedynczym standardowym obszarem komórki i czterema stałymi blokami. Warstwy masek są dostosowywane. Tutaj projektant może umieścić standardowe komórki w dowolnym miejscu na matrycy. Są one również znane jako C-BIC.

2). ASIC oparty na macierzy bramki

Ten typ pół-niestandardowego układu ASIC został wstępnie zdefiniowany tranzystory na płytce silikonowej. tj. projektant nie może zmienić położenia tranzystorów obecnych na matrycy. Tablica podstawowa to predefiniowany wzorzec tablicy bramek, a komórka podstawowa jest najmniejszą powtarzającą się komórką tablicy podstawowej.

Projektant ponosi odpowiedzialność tylko za zmianę połączenia między tranzystorami przy użyciu pierwszych kilku metalowych warstw matrycy. Projektant wybiera z biblioteki tablic bramek. Są one często nazywane tablicami zamaskowanych bramek. Układy ASIC oparte na macierzy bramkowej są trzech typów. Są to tablice bramek kanałowych, tablica bramek bezkanałowych i strukturalna tablica bramek.

a) Kanałowy układ bramek

W tego typu macierzy bramek przestrzeń na przewody pozostaje między rzędami tranzystorów. Są one podobne do CBIC, ponieważ pozostaje miejsce na wzajemne połączenia między blokami, ale w kanałowej macierzy bramkowej rzędy komórek mają stałą wysokość, podczas gdy w CBIC tę przestrzeń można regulować.

Channeled Gate Array

Niektóre z głównych cech tej tablicy bramek to - ta tablica bramek wykorzystuje predefiniowane odstępy między wierszami do wzajemnych połączeń. Czas produkcji wynosi od dwóch dni do dwóch tygodni.

b). Channel Less Gate Array

Nie ma wolnego miejsca na routing między rzędami komórek, jak widać w kanałowej tablicy bramek. Tutaj routing jest wykonywany z góry komórek tablicy bramkowej, ponieważ możemy dostosować połączenie między metalem 1 a tranzystorami. W przypadku routingu pozostawiamy tranzystory leżące na ścieżce routingu nieużywane. Czas realizacji zamówienia to około dwóch tygodni.

Channel Less Gate Array

do). Strukturalna tablica bramek

Ten typ tablicy bramek ma osadzony blok wraz z rzędami tablicy bramek, jak pokazano powyżej. Strukturalna tablica bramek ma wyższą wydajność obszarową CBIC. Podobnie jak macierz zamaskowanych bramek, mają one niższy koszt i szybszą realizację. Tutaj stały rozmiar wbudowanej funkcji stanowi ograniczenie dla strukturalnej tablicy bramek. Na przykład, czy ta tablica bramek zawiera obszar zarezerwowany dla kontrolera 32k bitowego, ale jeśli w aplikacji potrzebujemy tylko obszaru dla kontrolera 16k bitowego, pozostały obszar jest marnowany. Wszystkie tablice bramek mają czas realizacji od dwóch dni do dwóch tygodni i wszystkie mają dostosowane połączenia międzysieciowe.

Strukturalna tablica bramek

Programowalny ASIC

Istnieją dwa typy programowalnych układów ASIC. Są to PLD i FPGA

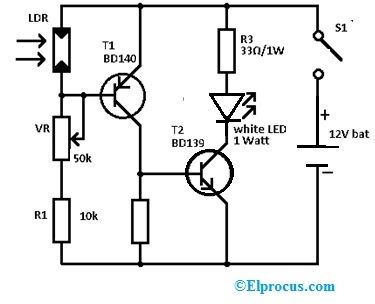

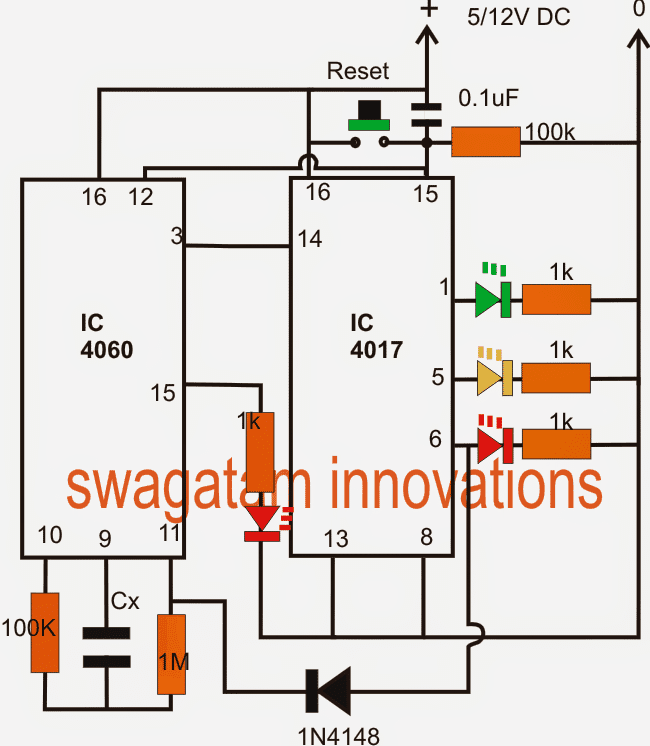

PLD (programowalne urządzenia logiczne)

Są to łatwo dostępne standardowe komórki. Możemy zaprogramować PLD, aby dostosować część aplikacji, więc są one traktowane jako ASIC. Możemy użyć różnych metod i oprogramowania do zaprogramowania PLD. Zawierają one regularną macierz komórek logicznych, zwykle programowalną logikę tablicową wraz z przerzutnikami lub zatrzaskami. Tutaj interkonekty są obecne jako jeden duży blok.

PROM jest typowym przykładem tego układu scalonego. EPROM wykorzystuje tranzystory MOS jako interkonekty, więc przykładając wysokie napięcie możemy je zaprogramować. PLD nie mają niestandardowych komórek logicznych ani połączeń międzysieciowych. Mają one szybki zwrot projektu.

Programowalne urządzenia logiczne

FPGA (tablica bramek programowalna przez użytkownika)

Gdzie PLD mają programowalną logikę tablicową jako komórki logiczne FPGA ma układ przypominający tablicę bramek. PLD są mniejsze i mniej złożone niż FPGA. Ze względu na swoją elastyczność i charakterystykę, FPGA zastępuje TTL w systemach mikroelektronicznych. Czas realizacji projektu to tylko kilka godzin.

Tablica bramek programowalna przez użytkownika

Rdzeń składa się z programowalnych podstawowych komórek logicznych, które mogą pełnić obie te funkcje kombinacyjne i logika sekwencyjna . Możemy programować komórki logiczne i łączyć je za pomocą pewnych metod. Podstawowe komórki logiczne są otoczone matrycą programowalnych połączeń, a rdzeń jest otoczony programowalnymi komórkami I / O.

FPGA zwykle składa się z konfigurowalnych bloków logicznych, konfigurowalnych bloków I / O, programowalnych połączeń, obwodów zegarowych, ALU, pamięci, dekoderów.

Widzieliśmy różne dostępne typy ASIC. Zobaczmy teraz, kiedy wszystkie te dostosowania i połączenia międzysieciowe są wykonywane podczas produkcji.

Przepływ projektowania układów scalonych specyficznych dla aplikacji (ASIC)

Projektowanie ASIC odbywa się krok po kroku. Ta kolejność kroków jest znana jako ASIC Design Pływ. Etapy projektowania przedstawiono na poniższym schemacie blokowym.

Przepływ projektowania ASIC

Wpis projektu: Na tym etapie mikroarchitektura projektu jest implementowana przy użyciu języków opisu sprzętu, takich jak VHDL, Verilog i System Verilog.

Synteza logiczna: Na tym etapie przy użyciu HDL przygotowywana jest lista sieci komórek logicznych, które mają być użyte, typów połączeń i wszystkich innych części wymaganych dla aplikacji.

Partycjonowanie systemu: Na tym etapie dzielimy matrycę o dużym rozmiarze na części o rozmiarze ASIC.

Symulacja przed układem: Na tym etapie wykonywany jest test symulacyjny, aby sprawdzić, czy projekt nie zawiera błędów.

Planowanie pięter: Na tym etapie na chipie układane są bloki listy sieci.

Umieszczenie: Na tym etapie ustalane jest położenie komórek wewnątrz bloku.

Wytyczanie: Na tym etapie rysowane są połączenia między blokami i komórkami. Ekstrakcja: na tym etapie określamy właściwości elektryczne, takie jak wartość rezystancji i wartość pojemności połączenia.

Symulacja po układzie: Przed oddaniem modelu do produkcji wykonuje się tę symulację, aby sprawdzić, czy system działa poprawnie wraz z obciążeniem połączenia.

Przykłady ASIC

Znając różne cechy ASIC, zobaczmy teraz kilka przykładów ASIC.

Standardowy układ ASIC oparty na ogniwach: LCB 300k, 500k od LSI Logic Company, SIG1, 2, 3 rodziny od ABB Hafo Inc., GCS90K z GCS Plessey.

Produkty Gate Array: AUA20K firmy Harris Semiconductor, SCX6Bxx firmy National Semiconductors, rodziny TGC / TEC firmy Texas Instruments.

Produkty PLD: Rodzina Advanced Micro Devices PAL, rodzina GAL firmy Philips Semiconductors, XC7300 i EPLD firmy XILINX.

Produkty FPGA: Serie XC2000, XC3000, XC4000, XC5000 firmy XILINX, pASIC1 firmy QuickLogic, MAX5000 firmy Altera.

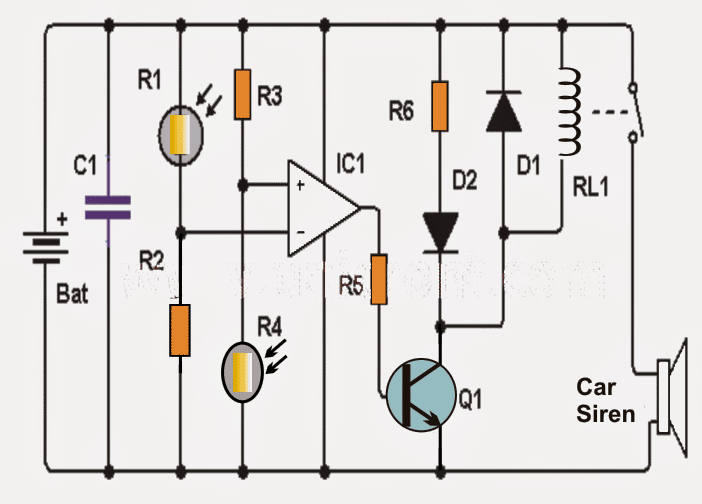

Zastosowania ASIC

Wyjątkowość ASIC zrewolucjonizowała sposób produkcji elektroniki. Zmniejszyły one rozmiary matrycy, jednocześnie zwiększając gęstość bramki logiczne za chip. Układy ASIC są zwykle preferowane w aplikacjach wysokiego poziomu. Układ ASIC jest używany jako rdzenie IP do satelitów, produkcji ROM, Mikrokontroler oraz różnego rodzaju aplikacje w branży medycznej i naukowej. Jedną z najpopularniejszych aplikacji ASIC jest BITCOIN MINER.

Bitcoin Miner

Wydobywanie kryptowalut wymaga większej mocy i szybkiego sprzętu. Procesor ogólnego przeznaczenia nie może zapewnić tak większej mocy obliczeniowej przy dużej szybkości. Kopacze bitcoinów ASIC to chipy wbudowane w specjalnie zaprojektowane płyty główne i zasilacze złożone w jedną całość. Jest to specjalnie zaprojektowany sprzęt aż do poziomu chipów do wydobywania bitcoinów. Jednostki te mogą wykonywać algorytm tylko jednej kryptowaluty. Przypuszczalnie dla innego rodzaju kryptowaluty potrzebujemy innego górnika.

Zalety i wady ASIC

Plik zalety ASIC obejmują następujące elementy.

- Mały rozmiar ASIC sprawia, że jest to duży wybór dla wyrafinowanych większych systemów.

- Ze względu na dużą liczbę obwodów zbudowanych na jednym chipie powoduje to aplikacje o dużej szybkości.

- ASIC ma niskie zużycie energii.

- Ponieważ są one układem na chipie, obwody są obecne obok siebie. Tak więc do połączenia różnych obwodów potrzebny jest bardzo minimalny routing.

- ASIC nie ma problemów z synchronizacją i konfiguracją postprodukcyjną.

Plik wady ASIC obejmują następujące elementy.

- Ponieważ są to chipy dostosowane do indywidualnych potrzeb, zapewniają małą elastyczność programowania.

- Ponieważ układy te muszą być projektowane od poziomu głównego, ich koszt w przeliczeniu na jednostkę jest wysoki.

- ASIC ma dłuższy czas na osiągnięcie marży rynkowej.

ASIC vs FPGA

Różnica między ASIC i FPGA obejmuje następujące elementy.

ASIC | FPGA |

| Nie da się przeprogramować | Przeprogramowalny |

| Preferowany do produkcji masowych | Preferowany do produkcji o małej objętości |

| Są one specyficzne dla aplikacji | Używany jako prototypy systemu |

| Energooszczędne wymaga mniej energii | Mniejsza energooszczędność wymaga większej mocy |

| Są to stałe obwody, których nie można od czasu do czasu aktualizować. | Doskonale nadaje się do zastosowań, w których obwód musi być od czasu do czasu aktualizowany, takich jak chipy telefonów komórkowych, stacje bazowe itp |

W związku z tym chodzi o przegląd Układ scalony specyficzny dla aplikacji . Wynalazek ASIC spowodował ogromną zmianę w sposobie używania elektroniki. ASIC używamy w naszym codziennym życiu w postaci różnych aplikacji. Jakie zastosowania ASIC spotkałeś? Z jakim typem ASIC pracowałeś?