W tym poście kompleksowo zrozumiemy, czym są bramki logiczne i jak działają. Przyjrzymy się podstawowej definicji, symbolom, tablicy prawdy, bramkom wielowejściowym, skonstruujemy również odpowiedniki bramek tranzystorowych, a na koniec omówimy różne istotne układy scalone CMOS.

Co to są bramki logiczne

Bramka logiczna w obwodzie elektronicznym może być wyrażona jako jednostka fizyczna reprezentowana przez funkcję boolowską.

Innymi słowy, bramka logiczna jest zaprojektowana do wykonywania funkcji logicznej przy użyciu jednego lub większej liczby wejść binarnych i do generowania pojedynczego wyjścia binarnego.

Elektroniczne bramki logiczne są zasadniczo konfigurowane i realizowane za pomocą bloków półprzewodnikowych lub elementów, takich jak diody lub tranzystory, które działają jak przełączniki ON / OFF o dobrze zdefiniowanym schemacie przełączania. Bramki logiczne ułatwiają kaskadowanie bramek w taki sposób, że z łatwością umożliwia komponowanie funkcji boolowskich, umożliwiając tworzenie fizycznych modeli wszystkich logiki Boole'a. To dodatkowo umożliwia zapisywanie algorytmów i matematyki przy użyciu logiki Boole'a.

Układy logiczne mogą wykorzystywać elementy półprzewodnikowe z zakresu multiplekserów, rejestrów, jednostek arytmetyczno-logicznych (ALU) i pamięci komputera, a nawet mikroprocesorów, obejmujących nawet setki milionów bramek logicznych. W dzisiejszej implementacji można znaleźć głównie tranzystory polowe (FET), używane do produkcji bramek logicznych, czego dobrym przykładem są tranzystory polowe typu metal-tlenek-półprzewodnik lub tranzystory MOSFET.

Zacznijmy samouczek od logiki AND.

Co to jest bramka logiczna „AND”?

Jest to bramka elektroniczna, której wyjście zmienia się w stan „wysoki” lub „1” lub „prawda” lub daje „dodatni sygnał”, gdy wszystkie wejścia bramek AND są „wysokie” lub „1” lub „prawda” lub „ sygnał pozytywny ”.

Na przykład: Powiedz w bramce AND z liczbą „n” wejść, jeśli wszystkie wejścia są „wysokie”, wyjście zmieni się na „wysokie”. Nawet jeśli jedno wejście ma stan „NISKI” lub „0”, „fałsz” lub „sygnał ujemny”, wyjście zmienia stan na „NISKI” lub „0” lub „fałsz” lub wydaje „sygnał ujemny”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja symbolu logiki AND:

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Wyrażenie boolowskie dla bramki logicznej AND: Wyjście „Y” jest pomnożeniem dwóch wejść „A” i „B”. (A.B) = Y.

Mnożenie boolowskie jest oznaczone kropką (.)

Jeśli „A” to „1”, a „B” to „1”, wynik to (A.B) = 1 x 1 = „1” lub „wysoki”

Jeśli „A” to „0”, a „B” to „1”, wyjście to (A.B) = 0 x 1 = „0” lub „Niski”

Jeśli „A” to „1”, a „B” to „0”, wyjście to (A.B) = 1 x 0 = „0” lub „Niski”

Jeśli „A” to „0”, a „B” to „0”, wyjście to (A.B) = 0 x 0 = „0” lub „Low”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Bramka z 3 wejściami „AND”:

Ilustracja 3 wejściowej bramki AND:

Bramki logiczne AND mogą mieć liczbę „n” wejść, co oznacza, że mogą mieć więcej niż dwa wejścia (bramki logiczne AND będą miały co najmniej dwa wejścia i zawsze jedno wyjście).

Dla bramki AND z 3 wejściami równanie Boole'a zmienia się w następujący sposób: (A.B.C) = Y, podobnie dla wejścia 4 i więcej.

Tabela prawdy dla logiki z 3 wejściami AND:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Logika wielowejściowa I bramki:

Dostępne w handlu bramki logiczne AND są dostępne tylko z 2, 3 i 4 wejściami. Jeśli mamy więcej niż 4 wejścia, musimy kaskadować bramki.

Możemy mieć sześć wejściowych bramek ORAZ poprzez kaskadowanie 2 wejściowych bramek ORAZ w następujący sposób:

Teraz równanie Boole'a dla powyższego obwodu przyjmuje postać Y = (A.B). (C.D). (E.F)

Mimo to wszystkie wspomniane reguły logiczne dotyczą powyższego obwodu.

Jeśli zamierzasz używać tylko 5 wejść z powyższych 6 wejść I bramek, możemy podłączyć rezystor podciągający do dowolnego jednego pinu i teraz stanie się on 5 wejściową bramką AND.

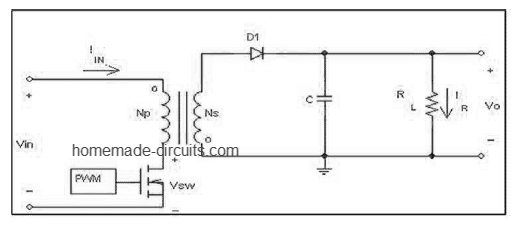

Bazująca na tranzystorach bramka logiczna I z dwoma wejściami:

Teraz wiemy, jak działa bramka logiczna AND, skonstruujmy 2-wejściową bramkę AND, używając dwóch tranzystorów NPN. Układy logiczne są zbudowane prawie w ten sam sposób.

Schemat dwóch tranzystorów AND bramki:

Do wyjścia „Y” można podłączyć diodę LED, jeśli poziom wyjściowy jest wysoki, dioda LED będzie się świecić (zacisk LED + Ve na „Y” z rezystorem 330 omów i ujemny do GND).

Kiedy przykładamy wysoki sygnał do podstawy dwóch tranzystorów, oba tranzystory włączają się, sygnał + 5V będzie dostępny na emiterze T2, więc wyjście staje się wysokie.

Jeśli którykolwiek z tranzystorów jest wyłączony, na emiterze T2 nie będzie dostępne napięcie dodatnie, ale z powodu rezystora obniżającego 1K na wyjściu będzie dostępne napięcie ujemne, więc wyjście jest określane jako niskie.

Teraz wiesz, jak zbudować własną logikę ORAZ bramę.

Quad AND bramki IC 7408:

Jeśli chcesz kupić logikę ORAZ bramę z rynku, otrzymasz powyższą konfigurację.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas potrzebny na zmianę wyjścia z NISKIEGO na WYSOKI i odwrotnie.

Opóźnienie propagacji od LOW do HIGH wynosi 27 nanosekund.

Opóźnienie propagacji od HIGH do LOW wynosi 19 nanosekund.

Inne powszechnie dostępne układy scalone bramki „AND”:

• 74LS08 Quad 2 wejścia

• 74LS11 Potrójne 3 wejścia

• 74LS21 Podwójne 4 wejścia

• CD4081 Quad, 2 wejścia

• CD4073 Potrójne 3 wejścia

• CD4082 Podwójne 4 wejścia

Aby uzyskać więcej informacji, zawsze możesz odwołać się do arkusza danych dla powyższych układów scalonych.

Jak Logic „Exclusive NOR” Funkcja bramki

W tym poście zajmiemy się bramką logiczną „Ex-NOR” lub bramką Exclusive-NOR. Przyjrzymy się podstawowej definicji, symbolom, tabeli prawdy, obwodowi równoważnemu Ex-NOR, realizacji Ex-NOR przy użyciu logiczne bramki NAND i na koniec przyjrzymy się quad 2 wejściowej bramce Ex-OR IC 74266.

Co to jest bramka „Exclusive NOR”?

Jest to bramka elektroniczna, której wyjście zmienia się w stan „wysoki” lub „1” lub „prawda” lub daje „dodatni sygnał”, gdy wejścia mają parzystą liczbę logicznych „1” (lub „prawda” lub „wysoki” lub „ sygnał pozytywny ”).

Na przykład: Wypowiedz bramkę typu Exclusive NOR z liczbą „n” wejść, jeśli wejścia są logiczne „HIGH” z 2 lub 4 lub 6 wejściami (parzysta liczba wejść „1s”), wyjście zmieni stan na „HIGH”.

Nawet jeśli nie zastosujemy logiki „high” do pinów wejściowych (tj. Zerowa liczba logiki „HIGH” i cała logika „LOW”), nadal „zero” jest liczbą parzystą, a wyjście zmienia stan na „HIGH”.

Jeśli liczba zastosowanych logicznych „1” jest ODD, wówczas wyjście zmienia stan na „LOW” (lub „0”, „fałsz” lub „sygnał ujemny”).

Jest to przeciwieństwo bramki logicznej „Exclusive OR”, w której wyjście zmienia stan na „WYSOKI”, gdy wejścia są nieparzystą liczbą logiczną „1s”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja bramki Logic „Exclusive NOR”:

Obwód odpowiadający bramce „Exclusive NOR”:

Powyższy obwód jest równoważny dla logiki Ex-NOR, która jest w zasadzie połączeniem bramki logicznej „Exclusive OR” i bramki logicznej „NOT”.

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Wyrażenie boolowskie dla bramki logicznej Ex-NOR: Y = (AB) ̅ + AB.

Jeśli „A” to „1”, a „B” to „1”, wyjście to ((AB) ̅ + AB) = 0 + 1 = „1” lub „WYSOKI”

Jeśli „A” to „0”, a „B” to „1”, wyjście to ((AB) ̅ + AB) = 0 + 0 = „0” lub „LOW”

Jeśli „A” to „1”, a „B” to „0”, wyjście to ((AB) ̅ + AB) = 0 + 0 = „0” lub „LOW”

Jeśli „A” to „0”, a „B” to „0”, wyjście to ((AB) ̅ + AB) = 1 + 1 = „1” lub „WYSOKI”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Bramka NOR z 3 wejściami:

Ilustracja 3 wejściowej bramki Ex-NOR:

Tablica prawdy dla 3-wejściowej bramki EX-OR:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Dla trójwejściowej bramki Ex-NOR równanie Boole'a przyjmuje postać: A ̅ (BC) ̅ + ABC ̅ + AB ̅C + A ̅BC.

Bramka logiczna „Ex-NOR” nie jest podstawową bramką logiczną, ale kombinacją różnych bramek logicznych. Bramka Ex-NOR może być zrealizowana za pomocą bramek logicznych „OR”, bramek logicznych „AND” i bramek logicznych „NAND” w następujący sposób:

Równoważny obwód dla bramki „Exclusive NOR”:

Powyższy projekt ma poważną wadę, potrzebujemy 3 różnych bramek logicznych, aby stworzyć jedną bramkę Ex-NOR. Ale możemy rozwiązać ten problem, wdrażając bramkę Ex-NOR tylko z bramkami logicznymi „NAND”, jest to również ekonomiczne w produkcji.

Ekskluzywna bramka NOR korzystająca z bramki NAND:

Ekskluzywne bramki NOR są używane do wykonywania skomplikowanych zadań obliczeniowych, takich jak operacje arytmetyczne, sumatory binarne, odejmowanie binarne, kontrolery parzystości i są używane jako komparatory cyfrowe.

Brama logiczna Exclusive-NOR IC 74266:

Jeśli chcesz kupić bramę logiczną Ex-NOR z rynku, dostaniesz w powyższej konfiguracji DIP.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas potrzebny na zmianę wyjścia z NISKIEGO na WYSOKI i odwrotnie po podaniu sygnału wejściowego.

Opóźnienie propagacji od LOW do HIGH wynosi 23 nanosekundy.

Opóźnienie propagacji od WYSOKI do NISKIE wynosi 23 nanosekundy.

Powszechnie dostępne układy scalone bramki „EX-NOR”:

74LS266 Quad 2 wejścia

CD4077 Quad 2 wejścia

Jak działa bramka NAND

W poniższym wyjaśnieniu zamierzamy zbadać cyfrową logiczną bramkę NAND. Przyjrzymy się podstawowej definicji, symbolom, tablicy prawdy, wielowejściowej bramce NAND, skonstruujemy tranzystorową 2-wejściową bramkę NAND, różne bramki logiczne wykorzystujące tylko bramkę NAND, a na koniec omówimy bramkę NAND IC 7400.

Co to jest bramka logiczna „NAND”?

Jest to bramka elektroniczna, której wyjście zmienia się na „LOW” lub „0” lub „false” lub daje „negatywny sygnał”, gdy wszystkie wejścia bramek NAND są „wysokie” lub „1” lub „prawda” lub „ sygnał pozytywny ”.

Na przykład: powiedz bramkę NAND z liczbą „n” wejść, jeśli wszystkie wejścia są „wysokie”, wyjście zmieni się na „NISKIE”. Nawet jeśli jedno wejście ma stan „NISKI” lub „0”, „fałsz” lub „sygnał ujemny”, wyjście zmienia stan na „WYSOKI” lub „1” lub „prawda” lub wydaje „sygnał dodatni”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja symbolu bramki Logic NAND:

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Ten symbol to bramka „AND” z inwersją „o”.

Obwód równoważny bramki logicznej „NAND”:

Bramka logiczna NAND jest połączeniem bramki logicznej „AND” i bramki logicznej „NOT”.

Wyrażenie boolowskie dla logicznej bramki NAND: Wyjście „Y” jest komplementarnym zwielokrotnieniem dwóch wejść „A” i „B”. Y = ((A.B) ̅)

Mnożenie boolowskie jest oznaczone kropką (.), A uzupełniające (inwersja) jest reprezentowane przez słupek (-) nad literą.

Jeśli „A” to „1”, a „B” to „1”, wyjście to ((A.B) ̅) = (1 x 1) ̅ = „0” lub „NISKI”

Jeśli „A” to „0”, a „B” to „1”, wyjście to ((A.B) ̅) = (0 x 1) ̅ = „1” lub „WYSOKI”

Jeśli „A” wynosi „1”, a „B” wynosi „0”, wyjście to ((A.B) ̅) = (1 x 0) ̅ = „1” lub „WYSOKI”

Jeśli „A” to „0”, a „B” to „0”, wyjście to ((A.B) ̅) = (0 x 0) ̅ = „1” lub „WYSOKI”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3-wejściowa bramka „NAND”:

Ilustracja 3 wejściowej bramki NAND:

Bramki logiczne NAND mogą mieć liczbę „n” wejść, co oznacza, że mogą mieć więcej niż dwa wejścia

(Bramki logiczne NAND będą miały co najmniej dwa wejścia i zawsze jedno wyjście).

Dla bramki NAND z 3 wejściami równanie Boole'a zmienia się w następujący sposób: ((A.B.C) ̅) = Y, podobnie dla 4 wejść i więcej.

Tabela prawdydla 3-wejściowej bramki logicznej NAND:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Bramki NAND z wieloma wejściami:

Dostępne w handlu bramki Logic NAND są dostępne tylko z 2, 3 i 4 wejściami. Jeśli mamy więcej niż 4 wejścia, musimy kaskadować bramki.

Na przykład możemy mieć cztery wejściowe bramki logiczne NAND, łącząc kaskadowo 5 dwóch wejściowych bramek NAND w następujący sposób:

Teraz równanie boolowskie dla powyższego obwodu staje się Y = ((A.B.C.D) ̅)

Mimo to wszystkie wspomniane reguły logiczne dotyczą powyższego obwodu.

Jeśli zamierzasz używać tylko 3 wejść z powyższej 4 wejściowej bramki NAND, możemy podłączyć rezystor podciągający do dowolnego jednego pinu i teraz stanie się on 3 wejściową bramką NAND.

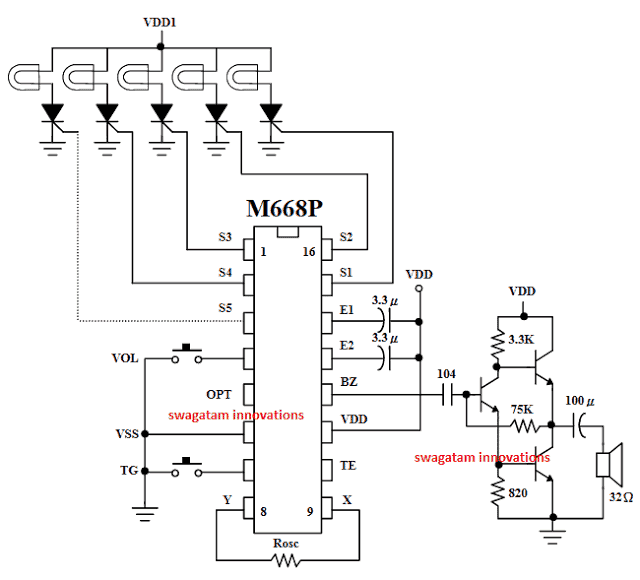

Bazująca na tranzystorach bramka logiczna NAND z dwoma wejściami:

Teraz wiemy, jak działa logiczna bramka NAND, skonstruujmy 2-wejściową bramkę NAND, używając dwóch

Tranzystory NPN. Układy logiczne są zbudowane prawie w ten sam sposób.

Schemat bramki NAND z dwoma tranzystorami:

Do wyjścia „Y” można podłączyć diodę LED, jeśli stan wyjściowy jest wysoki, dioda LED będzie się świecić (zacisk diody LED + Ve na „Y” z rezystorem 330 omów i ujemny do GND).

Kiedy podamy wysoki sygnał do bazy dwóch tranzystorów, oba tranzystory włączą się, sygnał masy będzie dostępny na kolektorze T1, więc wyjście zmieni się na „LOW”.

Jeśli którykolwiek z tranzystorów jest wyłączony, tj. Przykłada sygnał „LOW” do bazy, na kolektorze T1 nie będzie sygnału masy, ale ze względu na rezystor podciągający 1K na wyjściu będzie dostępny sygnał dodatni i wyjście będzie się obracać 'WYSOKI'.

Teraz wiesz, jak zbudować własną logiczną bramkę NAND.

Różne bramki logiczne korzystające z bramki NAND:

Bramka NAND jest również znana jako „uniwersalna bramka logiczna”, ponieważ za pomocą tej pojedynczej bramki możemy stworzyć dowolną logikę Boole'a. Jest to zaleta w przypadku wytwarzania układów scalonych o różnych funkcjach logicznych, a wytwarzanie pojedynczej bramki jest ekonomiczne.

Na powyższych schematach pokazano tylko 3 rodzaje bramek, ale możemy wykonać dowolną logikę boolowską.

Bramka Quad NAND IC 7400:

Jeśli chcesz kupić bramę logiczną NAND z rynku, otrzymasz powyższą konfigurację DIP.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas, w którym wyjście zmienia się z LOW na HIGH i odwrotnie po podaniu sygnału wejściowego.

Opóźnienie propagacji od LOW do HIGH wynosi 22 nanosekundy.

Opóźnienie propagacji od WYSOKI do NISKIE wynosi 15 nanosekund.

Dostępnych jest kilka innych układów scalonych bramek NAND:

- 74LS00 Quad 2 wejścia

- 74LS10 Potrójne 3 wejścia

- 74LS20 Podwójne 4 wejścia

- 74LS30 Pojedyncze 8 wejść

- CD4011 Quad 2 wejścia

- CD4023 Potrójne 3 wejścia

- CD4012 Podwójne 4 wejścia

Jak działa NOR Gate

Tutaj zajmiemy się cyfrową logiką bramki NOR. Przyjrzymy się podstawowej definicji, symbolom, tablicy prawdy, wielowejściowej bramce NOR, będziemy budować 2-wejściową bramkę NOR opartą na tranzystorze, różne bramki logiczne wykorzystujące tylko bramkę NOR i na koniec przyjrzymy się bramce NOR IC 7402.

Co to jest bramka logiczna „NOR”?

Jest to bramka elektroniczna, której wyjście zmienia stan na „WYSOKI” lub „1” lub „prawda” lub daje „dodatni sygnał”, gdy wszystkie wejścia bramek NOR są „NISKIE” lub „0” lub „fałszywe” lub „ sygnał ujemny ”.

Na przykład: Powiedz bramkę NOR z liczbą „n” wejść, jeśli wszystkie wejścia są „LOW”, wyjście zmieni się na „HIGH”. Nawet jeśli jedno z wejść ma stan „WYSOKI” lub „1”, „prawda” lub „sygnał dodatni”, wyjście zmienia stan na „NISKI”, „0” lub „fałsz”, lub wydaje „sygnał ujemny”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja symbolu bramki Logic NOR:

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Ten symbol to bramka „OR” z inwersją „o”.

Obwód równoważny bramki logicznej „NOR”:

Bramka logiczna NOR jest połączeniem bramki logicznej „OR” i bramki logicznej „NIE”.

Wyrażenie boolowskie dla logicznej bramki NOR: Wyjście „Y” jest uzupełnieniem dwóch wejść „A” i „B”. Y = ((A + B) ̅)

Dodatek logiczny jest oznaczony (+), a dopełniacz (inwersja) jest reprezentowany przez słupek (-) nad literą.

Jeśli „A” to „1”, a „B” to „1”, wyjście to ((A + B) ̅) = (1+ 1) ̅ = „0” lub „LOW”

Jeśli „A” to „0”, a „B” to „1”, wyjście to ((A + B) ̅) = (0+ 1) ̅ = „0” lub „LOW”

Jeśli „A” wynosi „1”, a „B” wynosi „0”, wyjście to ((A + B) ̅) = (1+ 0) ̅ = „0” lub „LOW”

Jeśli „A” to „0”, a „B” to „0”, wyjście to ((A + B) ̅) = (0+ 0) ̅ = „1” lub „WYSOKI”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Bramka 3-wejściowa „NOR”:

Ilustracja 3 wejściowej bramki NOR:

Bramki logiczne NOR mogą mieć liczbę „n” wejść, co oznacza, że mogą mieć więcej niż dwa wejścia (bramki logiczne NOR będą miały co najmniej dwa wejścia i zawsze jedno wyjście).

Dla bramki NOR z 3 wejściami równanie Boole'a zmienia się w następujący sposób: ((A + B + C) ̅) = Y, podobnie dla 4 wejść i więcej.

Tabela prawdy dla bramki NOR z 3 wejściami:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Bramki NOR z wieloma wejściami:

Dostępne w handlu bramki Logic NOR są dostępne tylko z 2, 3 i 4 wejściami. Jeśli mamy więcej niż 4 wejścia, musimy kaskadować bramki.

Na przykład, możemy mieć cztery wejściowe bramki NOR poprzez kaskadowanie 5 dwóch wejściowych bramek NOR w następujący sposób:

Teraz równanie Boole'a dla powyższego obwodu staje się Y = ((A + B + C + D) ̅)

Mimo to wszystkie wspomniane reguły logiczne dotyczą powyższego obwodu.

Jeśli zamierzasz używać tylko 3 wejść z powyższej 4 wejściowej bramki NOR, możemy podłączyć rezystor obniżający do dowolnego z pinów i teraz stanie się on 3 wejściową bramką NOR.

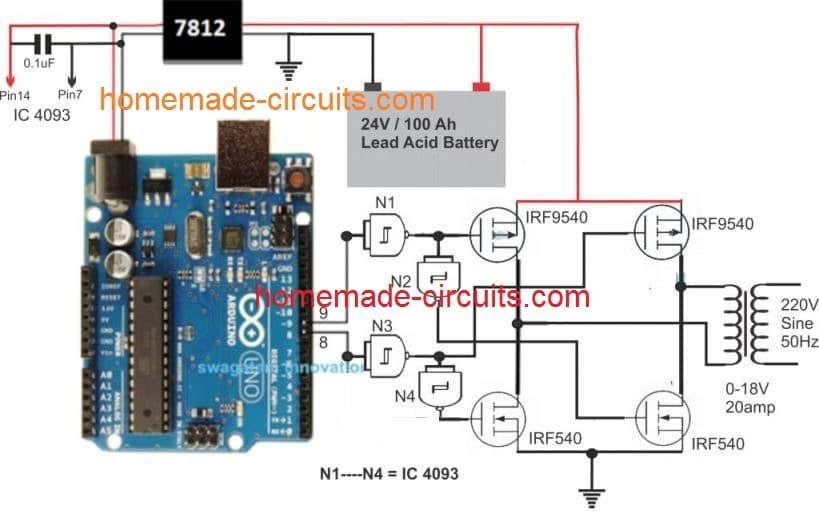

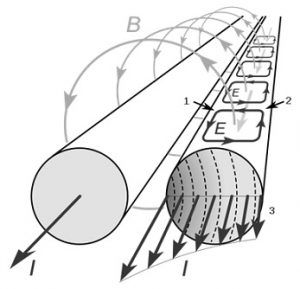

Bazująca na tranzystorach dwu wejściowa bramka NOR:

Teraz wiemy, jak funkcjonuje logiczna bramka NOR, skonstruujmy 2-wejściową bramkę NOR, używając dwóch tranzystorów NPN. Układy logiczne są zbudowane prawie w ten sam sposób.

Schemat bramki NOR z dwoma tranzystorami:

Do wyjścia „Y” można podłączyć diodę LED, jeśli stan wyjściowy jest wysoki, dioda LED będzie się świecić (zacisk diody LED + Ve na „Y” z rezystorem 330 omów i ujemny do GND).

Kiedy podamy sygnał „HIGH” do bazy dwóch tranzystorów, oba tranzystory włączą się i sygnał masy będzie dostępny na kolektorze T1 i T2, a więc wyjście zmieni stan na „LOW”.

Jeśli zastosujemy „HIGH” na którymkolwiek z tranzystorów, to nadal na wyjściu będzie dostępny sygnał ujemny, powodując, że wyjście przejdzie w stan „LOW”.

Jeśli podamy sygnał „LOW” do bazy dwóch tranzystorów, to oba wyłączą się, ale ze względu na rezystor podciągający wyjście zmieni stan na „HIGH”.

Teraz wiesz, jak zbudować własną logiczną bramkę NOR.

Różne bramki logiczne używające bramki NOR:

UWAGA: NAND i NOR to dwie bramki zwane inaczej bramkami uniwersalnymi.

Bramka NOR jest również „uniwersalną bramką logiczną”, ponieważ za pomocą tej pojedynczej bramki możemy stworzyć dowolną logikę Boole'a. Jest to zaleta w przypadku wytwarzania układów scalonych o różnych funkcjach logicznych, a wytwarzanie pojedynczej bramki jest ekonomiczne, to samo dotyczy bramki NAND.

Na powyższych schematach przedstawiono tylko 3 typy bramek, ale możemy wykonać dowolną logikę boolowską.

Poczwórna bramka NOR IC 7402:

Jeśli chcesz kupić bramę logiczną NOR z rynku, otrzymasz powyższą konfigurację DIP.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas, w którym wyjście zmienia się z LOW na HIGH i odwrotnie po podaniu sygnału wejściowego.

Opóźnienie propagacji od LOW do HIGH wynosi 22 nanosekundy.

Opóźnienie propagacji od WYSOKI do NISKIE wynosi 15 nanosekund.

Dostępnych jest kilka innych układów scalonych bramek NOR:

- 74LS02 Quad 2 wejścia

- 74LS27 Potrójne 3 wejścia

- 74LS260 Podwójne 4 wejścia

- CD4001 Quad 2 wejścia

- CD4025 Potrójne 3 wejścia

- CD4002 Podwójne 4 wejścia

Logika NIE Brama

W tym poście zamierzamy zbadać bramę logiczną „NIE”. Dowiemy się o jego podstawowej definicji, symbolu, tablicy prawdy, odpowiednikach bramek NAND i NOR, falownikach Schmitta, oscylatorze bramkowym Schmitta NIE, bramce NIE używającej tranzystora, a na koniec przyjrzymy się inwerterowi logicznemu NIE bramce IC 7404.

Zanim zaczniemy przyglądać się szczegółom bramki logicznej NOT, która jest również nazywana cyfrowym inwerterem, nie wolno mylić z „falownikami mocy”, które są używane w zasilaczach słonecznych lub rezerwowych w domu lub biurze.

Czym jest bramka logiczna „NIE”?

Jest to bramka logiczna z pojedynczym wejściem i jednym wyjściem, której wyjście jest uzupełnieniem wejścia.

Powyższa definicja mówi, że jeśli wejście ma stan „WYSOKI” lub „1”, „prawda” lub „sygnał dodatni”, na wyjściu będzie stan „NISKI” lub „0” lub „fałszywy” lub „sygnał ujemny”.

Jeśli wejście jest „NISKIE” lub „0”, „fałszywe” lub „sygnał ujemny”, wyjście zostanie odwrócone na „WYSOKI” lub „1” lub „prawda” lub „sygnał dodatni”

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja bramki Logic NOT:

Załóżmy, że „A” to wejście, a „Y” to wyjście, równanie Boole'a dla bramki logicznej NOT to: Ā = Y.

Równanie stwierdza, że wyjście jest odwróceniem wejścia.

Tabela prawdy dla bramki logicznej NIE:

| DO (WEJŚCIE) | Y (WYNIK) |

| 0 | 1 |

| 1 | 0 |

Bramki nie zawsze będą miały jedno wejście (i zawsze będą miały jedno wyjście), jest to klasyfikowane jako urządzenia decyzyjne. Symbol „o” na końcu trójkąta oznacza uzupełnienie lub inwersję.

Ten symbol „o” nie jest ograniczony tylko do bramki logicznej „NIE”, ale może być również używany przez dowolne bramki logiczne lub dowolny obwód cyfrowy. Jeśli na wejściu jest „o”, oznacza to, że wejście jest aktywne w stanie niskim.

Aktywny-niski: Wyjście staje się aktywne (aktywacja tranzystora, diody LED lub przekaźnika itp.), Gdy podane jest wejście „LOW”.

Odpowiedniki bramek NAND i NOR:

Bramka „NOT” może być zbudowana przy użyciu bramek logicznych „NAND” i logicznych „NOR” poprzez połączenie wszystkich pinów wejściowych, dotyczy to bramek z 3, 4 i wyższymi pinami wejściowymi.

Bramka logiczna „NIE” oparta na tranzystorze:

Logika „NIE” może być zbudowana z tranzystora NPN i rezystora 1K. Jeśli podamy sygnał „HIGH” do bazy tranzystora, to masa zostanie połączona z kolektorem tranzystora, a tym samym wyjście zmieni stan na „LOW”.

Jeśli podamy sygnał „LOW” do bazy tranzystora, tranzystor pozostanie WYŁĄCZONY i nie będzie podłączony do masy, ale wyjście będzie „WYSOKIE” przez rezystor podciągający podłączony do Vcc. W ten sposób możemy stworzyć bramkę logiczną „NIE” za pomocą tranzystora.

Falowniki Schmitta:

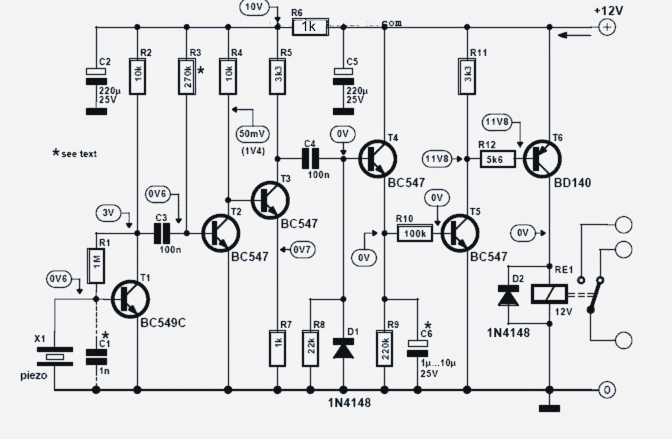

Zbadamy tę koncepcję z automatyczną ładowarką akumulatorów, aby wyjaśnić wykorzystanie i działanie falowników Schmitta. Weźmy na przykład procedurę ładowania akumulatora litowo-jonowego.

Akumulator litowo-jonowy 3,7 V jest ładowany, gdy akumulator osiągnie napięcie od 3 V do 3,2 V, podczas ładowania napięcie akumulatora stopniowo rośnie i akumulator należy odciąć przy 4,2 V.Po naładowaniu napięcie w obwodzie otwartym akumulatora spada około 4,0 V .

Czujnik napięcia mierzy granicę odcięcia i uruchamia przekaźnik, aby zatrzymać ładowanie. Ale gdy napięcie spadnie poniżej 4,2 V, ładowarka wykrywa, że nie jest naładowana i zaczyna ładować do 4,2 V i odcina, ponownie napięcie akumulatora spada do 4,0 V i ponownie rozpoczyna ładowanie i to szaleństwo w kółko.

To szybko zabije baterię, aby rozwiązać ten problem, potrzebujemy niższego poziomu progu lub „LTV”, aby bateria nie zaczęła się ładować, dopóki bateria nie spadnie do 3 V do 3,2 V. Górne napięcie progowe lub „UTV” to W tym przykładzie 4,2 V.

Falownik Schmitta przełącza swój stan wyjściowy, gdy napięcie przekracza napięcie górnego progu i pozostaje taki sam, dopóki wejście nie osiągnie dolnego napięcia progowego.

Podobnie, gdy wejście przekroczy dolne napięcie progowe, wyjście pozostaje takie samo, dopóki wejście nie osiągnie górnego napięcia progowego.

Nie zmieni swojego stanu między LTV a UTV.

Teraz, z tego powodu, włączanie / wyłączanie będzie znacznie płynniejsze, a niepożądane oscylacje zostaną usunięte, a także obwód będzie bardziej odporny na szum elektryczny.

Oscylator bramkowy Schmitt NOT:

Powyższy obwód jest oscylatorem, który wytwarza falę prostokątną przy 33% cyklu pracy. Początkowo kondensator jest w stanie rozładowanym, a sygnał masy będzie dostępny na wejściu bramki NOT.

Wyjście staje się dodatnie i ładuje kondensator przez rezystor „R”, kondensator ładuje się do górnego progu napięcia falownika i zmienia stan, wyjście zamienia sygnał ujemny i kondensator zaczyna się rozładowywać przez rezystor „R”, aż napięcie kondensatora osiągnie niższy poziom progowy i zmienia stan, wyjście staje się dodatnie i ładuje kondensator.

Cykl ten powtarza się tak długo, jak długo obwód jest zasilany.

Częstotliwość powyższego oscylatora można obliczyć: F = 680 / RC

Gdzie F to częstotliwość.

R jest oporem w omach.

C to pojemność w faradzie.

Konwerter fal prostokątnych:

Powyższy obwód konwertuje sygnał sinusoidalny na prostokątny, w rzeczywistości może przekształcić dowolne fale analogowe w prostokątne.

Dwa rezystory R1 i R2 działają jako dzielnik napięcia, jest to wykorzystywane do uzyskania punktu polaryzacji, a kondensator blokuje wszelkie sygnały DC.

Jeśli sygnał wejściowy przekroczy górny poziom progu lub poniżej dolnego poziomu progu, wyjście zostanie przełączone

NISKA lub WYSOKA w zależności od sygnału, generuje falę prostokątną.

Falownik bramowy IC 7404 NOT:

IC 7404 jest jednym z najczęściej używanych układów logicznych NOT bramki. Ma 14 pinów, pin # 7 to masa, a pin # 14 to Vcc. Napięcie robocze wynosi od 4,5 V do 5 V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas potrzebny bramce do przetworzenia wyjścia po podaniu sygnału wejściowego.

W logice bramka „NIE” potrzebuje około 22 nanosekund, aby zmienić swój stan z WYSOKI na NISKI i odwrotnie.

Istnieje kilka innych układów logicznych „NOT bramek”:

• 74LS04 Hex Inverting NOT Gate

• 74LS14 Hex Schmitt Inverting NOT Gate

• 74LS1004 Hex odwracające sterowniki

• CD4009 Hex Inverting NOT Gate

• CD4069 Hex Inverting NOT Gate

Jak działa bramka OR

Teraz przyjrzyjmy się cyfrowym bramkom OR. Przyjrzymy się podstawowej definicji, symbolom, tablicy prawdy, bramce wielowejściowej OR, skonstruujemy bramkę OR z 2 wejściami tranzystorowymi i na koniec omówimy bramkę OR IC 7432.

Co to jest bramka logiczna „OR”?

Jest to bramka elektroniczna, której wyjście zmienia się na „LOW” lub „0” lub „false” lub wydaje „negatywny sygnał”, gdy wszystkie wejścia bramek OR są „LOW” lub „0” lub „false” lub „ sygnał ujemny ”.

Na przykład: Powiedz bramkę OR z liczbą „n” wejść, jeśli wszystkie wejścia są „LOW”, wyjście zmieni się na „LOW”. Nawet jeśli jedno z wejść ma stan „WYSOKI” lub „1”, „prawda” lub „sygnał dodatni”, wyjście zmienia stan na „WYSOKI” lub „1” lub „prawda” lub wydaje „sygnał dodatni”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja symbolu logiki LUB bramki:

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Wyrażenie logiczne dla bramki logicznej OR: Wyjście „Y” jest sumą dwóch wejść „A” i „B”, (A + B) = Y.

Dodatek boolowski jest oznaczony przez (+)

Jeśli „A” to „1”, a „B” to „1”, wynik to (A + B) = 1 + 1 = „1” lub „wysoki”

Jeśli „A” to „0”, a „B” to „1”, to na wyjściu (A + B) = 0 + 1 = „1” lub „wysoki”

Jeśli „A” to „1”, a „B” to „0”, wyjście to (A + B) = 1 + 0 = „1” lub „wysoki”

Jeśli „A” to „0”, a „B” to „0”, wyjście to (A + B) = 0 + 0 = „0” lub „Niski”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Bramka z 3 wejściami „LUB”:

Ilustracja 3 wejściowej bramki OR:

Bramki logiczne OR mogą mieć liczbę „n” wejść, co oznacza, że mogą mieć więcej niż dwa wejścia (bramki logiczne OR będą miały co najmniej dwa wejścia i zawsze jedno wyjście).

Dla bramki OR z 3 wejściami, równanie Boole'a zmienia się w następujący sposób: (A + B + C) = Y, podobnie dla 4 wejść i więcej.

Tabela prawdy dla logiki z 3 wejściami OR:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Logika wielowejściowa LUB bramki:

Dostępne w handlu bramki logiczne OR są dostępne tylko z 2, 3 i 4 wejściami. Jeśli mamy więcej niż 4 wejścia, musimy kaskadować bramki.

Możemy mieć sześć wejściowych bramek OR poprzez kaskadowanie 2 wejściowych bramek OR w następujący sposób:

Teraz równanie Boole'a dla powyższego obwodu staje się Y = (A + B) + (C + D) + (E + F)

Mimo to wszystkie wspomniane reguły logiczne dotyczą powyższego obwodu.

Jeśli zamierzasz użyć tylko 5 wejść z powyższych 6 wejść OR, możemy podłączyć rezystor obniżający do dowolnego pinu i teraz stanie się on 5 wejściową bramką OR.

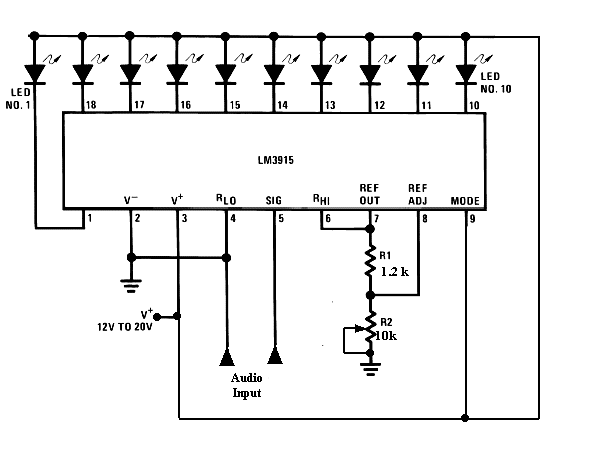

Bazująca na tranzystorach bramka logiczna OR z dwoma wejściami:

Teraz już wiemy, jak działa logiczna bramka OR, skonstruujmy 2-wejściową bramkę OR, używając dwóch tranzystorów NPN. Układy logiczne są zbudowane prawie w ten sam sposób.

Schemat dwóch tranzystorów OR:

Do wyjścia „Y” można podłączyć diodę LED, jeśli poziom wyjściowy jest wysoki, dioda LED będzie się świecić (zacisk LED + Ve na „Y” z rezystorem 330 omów i ujemny do GND).

Kiedy przykładamy sygnał LOW do bazy dwóch tranzystorów, oba tranzystory wyłączają się, sygnał masy będzie dostępny na emiterze T2 / T1 przez rezystor pull-down 1k, a więc wyjście zmieni się na LOW.

Jeśli którykolwiek z tranzystorów jest włączony, na emiterze T2 / T1 będzie dostępne napięcie dodatnie, a zatem wyjście zmieni stan na WYSOKI.

Teraz wiesz, jak zbudować własną logikę OR.

Quad OR bramka IC 7432:

Jeśli chcesz kupić bramę logiczną LUB z rynku, otrzymasz powyższą konfigurację.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas potrzebny na zmianę wyjścia z NISKIEGO na WYSOKI i odwrotnie.

Opóźnienie propagacji od LOW do HIGH wynosi 7,4 nanosekundy przy 25 stopniach Celsjusza.

Opóźnienie propagacji od WYSOKI do NISKIE wynosi 7,7 nanosekund przy 25 stopniach Celsjusza.

• 74LS32 Quad 2 wejścia

• CD4071 Quad 2 wejścia

• CD4075 Potrójne 3 wejścia

• CD4072 Podwójne 4 wejścia

Logic Exclusive - OR Gate

W tym poście zajmiemy się logiczną bramką XOR lub bramką Exclusive-OR. Przyjrzymy się podstawowej definicji, symbolom, tablicy prawdy, obwodzie równoważnym XOR, realizacji XOR za pomocą logicznych bramek NAND, a na koniec przyjrzymy się poczwórnej 2 wejściowej bramce Ex-OR IC 7486.

W poprzednich postach dowiedzieliśmy się o trzech podstawowych bramkach logicznych „AND”, „OR” i „NOT”. Dowiedzieliśmy się również, że korzystając z tych trzech podstawowych bramek możemy zbudować dwie nowe bramki logiczne „NAND” i „NOR”.

Istnieją jeszcze dwie bramki logiczne, chociaż te dwie nie są podstawowymi bramkami, ale są zbudowane przez połączenie innych bramek logicznych, a jego równanie Boole'a jest tak istotne i bardzo przydatne, że jest uważane za odrębne bramki logiczne.

Te dwie bramki logiczne to bramka „Exclusive OR” i „Exclusive NOR”. W tym poście zajmiemy się wyłącznie logiką Exclusive OR gate.

Co to jest bramka „Exclusive OR”?

Jest to bramka elektroniczna, której wyjście zmienia się w stan „wysoki” lub „1” lub „prawda” lub wydaje „dodatni sygnał”, gdy dwa wejścia logiczne są różne względem siebie (dotyczy to tylko dwóch 2 wejść Ex -LUB brama).

Na przykład: Powiedz bramkę Exclusive OR z 'dwoma' wejściami, jeśli jeden z pinów wejściowych A jest „HIGH”, a pin wejściowy B jest „LOW”, wtedy wyjście zmieni się na „HIGH” lub „1” lub „true” lub „Pozytywny sygnał”.

Jeśli oba wejścia mają ten sam poziom logiczny, tj. Oba piny „HIGH” lub oba piny „LOW”, wyjście zmieni stan na „LOW” lub „0” lub „false” lub „ujemny sygnał”.

Uwaga:

Terminy „wysoki”, „1”, „sygnał dodatni”, „prawda” są zasadniczo takie same (sygnał dodatni to sygnał dodatni akumulatora lub zasilacza).

Terminy „NISKI”, „0”, „sygnał ujemny”, „fałsz” są zasadniczo takie same (sygnał ujemny to sygnał ujemny akumulatora lub zasilacza).

Ilustracja bramki Logic Exclusive OR:

Tutaj „A” i „B” to dwa wejścia, a „Y” jest wyprowadzane.

Wyrażenie boolowskie dla bramki logicznej Ex-OR: Y = (A.) ̅B + A.B ̅

Jeśli „A” to „1”, a „B” to „1”, wynik to (A ̅.B + A.B ̅) = 0 x 1 + 1 x 0 = „1” lub „LOW”

Jeśli „A” to „0”, a „B” to „1”, wynik to (A ̅.B + A.B ̅) = 1 x 1 + 0 x 0 = „1” lub „WYSOKI”

Jeśli „A” wynosi „1”, a „B” wynosi „0”, wynik wynosi (A ̅.B + A.B ̅) = 0 x 0 + 1 x 1 = „1” lub „WYSOKI”

Jeśli „A” to „0”, a „B” to „0”, wyjście to (A ̅.B + A.B ̅) = 1 x 0 + 0 x 1 = „0” lub „Low”

Powyższe warunki są uproszczone w tabeli prawdy.

Tabela prawdy (dwa wejścia):

| A (wejście) | B (WEJŚCIE) | Y (wyjście) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

W powyższej logice dwóch wejść Ex-OR, jeśli dwa wejścia są różne, tj. „1” i „0”, wyjście zmienia stan na „WYSOKI”. Ale z 3 lub więcej logikami wejściowymi Ex-OR lub ogólnie wyjście Ex-OR zmienia się na „WYSOKI” tylko wtedy, gdy liczba ODD logiki „WYSOKA” jest przyłożona do bramki.

Na przykład: Jeśli mamy 3 wejściową bramkę Ex-OR, jeśli zastosujemy logikę „WYSOKA” tylko do jednego wejścia (nieparzysta liczba logiki „1”), wyjście zmieni stan na „WYSOKI”. Jeśli zastosujemy logikę „HIGH” do dwóch wejść (jest to parzysta liczba logiki „1”), wyjście zmieni stan na „LOW” i tak dalej.

3 wejścia wyłączne LUB bramka:

Ilustracja 3 wejściowej bramki EX-OR:

Tablica prawdy dla 3-wejściowej bramki EX-OR:

| A (WEJŚCIE) | B (WEJŚCIE) | C (WEJŚCIE) | Y (WYJŚCIE) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Dla 3-wejściowej bramki Ex-OR równanie Boole'a staje się: A (BC) ̅ + A ̅BC ̅ + (AB) ̅C + ABC

Jak opisaliśmy wcześniej, bramka logiczna „Ex-OR” nie jest podstawową bramką logiczną, ale kombinacją różnych bramek logicznych. Bramka Ex-OR może być zrealizowana za pomocą bramki logicznej „OR”, bramki logicznej „AND” i bramki logicznej „NAND” w następujący sposób:

Równoważny obwód dla bramki „Exclusive OR”:

Powyższy projekt ma poważną wadę, potrzebujemy 3 różnych bramek logicznych do wykonania jednej bramki Ex-OR. Ale możemy rozwiązać ten problem, wdrażając bramkę Ex-OR tylko z logicznymi bramkami NAND, jest to również ekonomiczne w produkcji.

Ekskluzywna bramka OR korzystająca z bramki NAND:

Ekskluzywne bramki OR służą do wykonywania skomplikowanych zadań obliczeniowych, takich jak operacje arytmetyczne, pełne sumatory, półsumatory, mogą również dostarczać funkcjonalność.

Logic Exclusive OR Gate IC 7486:

Jeśli chcesz kupić bramę logiczną Ex-OR z rynku, otrzymasz powyższą konfigurację DIP.

Ma 14 pinów, pin # 7 i pin # 14 to odpowiednio GND i Vcc. Działa przy 5V.

Opóźnienie propagacji:

Opóźnienie propagacji to czas potrzebny na zmianę wyjścia z NISKIEGO na WYSOKI i odwrotnie po podaniu sygnału wejściowego.

Opóźnienie propagacji od LOW do HIGH wynosi 23 nanosekundy.

Opóźnienie propagacji od WYSOKI do NISKIE wynosi 17 nanosekund.

Powszechnie dostępne układy scalone bramki „EX-OR”:

- 74LS86 Quad 2 wejścia

- CD4030 Quad 2 wejścia

Mam nadzieję, że powyższe szczegółowe wyjaśnienie mogło pomóc ci zrozumieć, czym są bramki logiczne i jak działają bramki logiczne, jeśli nadal masz jakieś pytania? Prosimy o wyrażenie w komentarzu, możesz otrzymać szybką odpowiedź.

Poprzedni: Obwód testera upływu kondensatora - szybko znajdź nieszczelne kondensatory Dalej: Bufor cyfrowy - praca, definicja, tablica prawdy, podwójna inwersja, fan-out