Proces projektowania sprzętu cyfrowego uległ intensywnym przemianom w ciągu ostatnich kilku lat. Tak więc małe obwody cyfrowe można zaimplementować za pomocą PAL i PLA. Każde urządzenie jest używane do realizacji różnych obwodów które nie wymagają więcej niż liczba i / ps, o / ps i warunków produktu, które są oferowane w określonym chipie. Te chipy są nieadekwatne do dość skromnych rozmiarów, zwykle obsługują wspólną liczbę wejść i wyjść nie większą niż 32. Do projektowania tych obwodów, które wymagają więcej wejść i wyjść, można zastosować wiele PLA / PAL lub też bardziej klasyczny typ chip może być używany jako CPLD (złożone programowalne urządzenie logiczne). Układ CPLD zawiera kilka bloków obwodów na jednym chipie z wewnętrznymi zasobami okablowania do podłączenia bloków obwodów. Każdy blok obwodu jest porównywalny z PLA lub PAL.

Co to jest złożone programowalne urządzenie logiczne?

Akronim CPLD to „Złożone programowalne urządzenia logiczne”, to jest jeden rodzaj układu scalonego że projektanci aplikacji projektują sprzęt cyfrowy, taki jak telefony komórkowe Mogą one obsługiwać świadomie wyższe projekty niż SPLD (proste programowalne urządzenia logiczne), ale oferują mniej logiki niż układy FPGA ( tablice bramek programowalne przez użytkownika CPLD zawierają liczne bloki logiczne, każdy z bloków zawiera 8-16 makrokomórek. Ponieważ każdy blok logiczny wykonuje określoną funkcję, wszystkie makrokomórki w bloku logicznym są w pełni połączone. W zależności od zastosowania, bloki te mogą być ze sobą połączone lub nie.

Złożone programowalne urządzenie logiczne

Większość CPLD (złożone programowalne urządzenia logiczne) ma makrokomórki z sumą funkcji logicznych i FF (przerzutnik) . W zależności od chipa, kombinatoryczna funkcja logiczna obsługuje od 4 do 16 terminów produktowych z wbudowanym wachlarzem. CPLD różnią się również pod względem rejestrów przesuwnych i bramek logicznych. Z tego powodu zamiast układów FPGA można zastosować układy CPLD z ogromną liczbą bramek logicznych. Inna specyfikacja CPLD określa liczbę terminów produktu, które może wykonać makrokomórka. Terminy produktowe są wynikiem sygnałów cyfrowych, które wykonują określoną funkcję logiczną.

CPLD są dostępne w kilku formach pakietów IC i rodzinach logicznych. CPLD różnią się również pod względem napięcia zasilania, prądu roboczego, prądu czuwania i rozpraszania mocy. Ponadto są one dostępne z różnymi ilościami pamięci i różnymi rodzajami obsługi pamięci. Zwykle pamięć jest wyrażana w bitach / megabitach. Obsługa pamięci obejmuje ROM, RAM i dwuportową pamięć RAM. Składa się również z pamięci CAM (pamięć adresowalna zawartości), a także pamięci FIFO (pierwsze weszło, pierwsze wyszło) i LIFO (ostatnie wejście, ostatnie wyszło).

Architektura złożonego programowalnego urządzenia logicznego

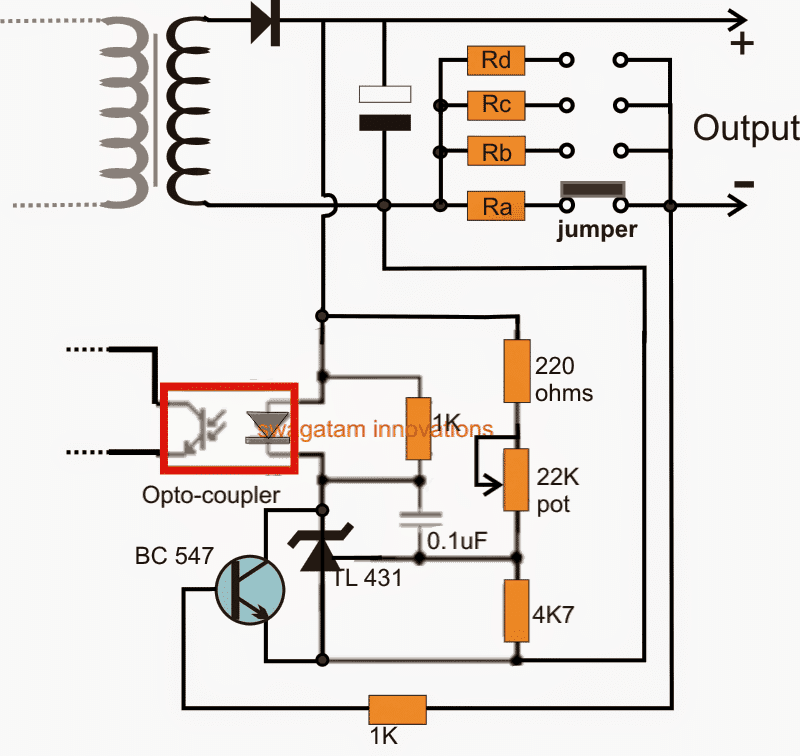

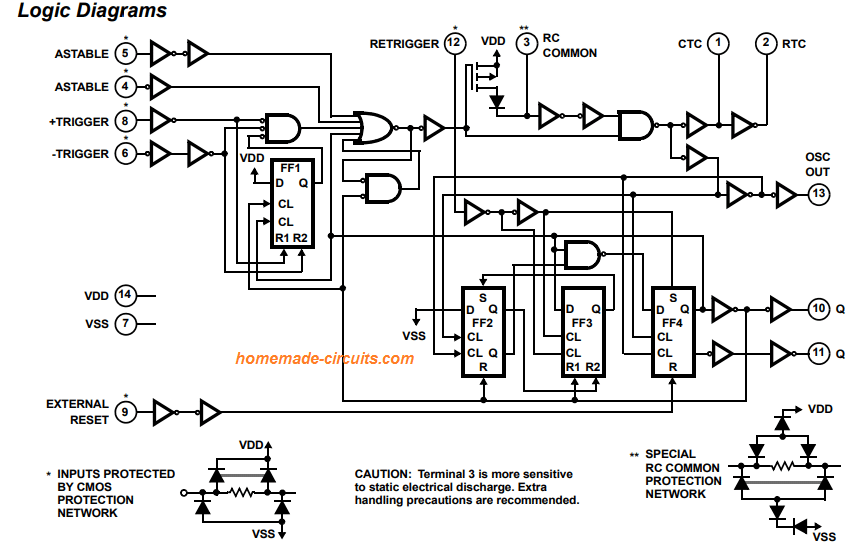

Złożone programowalne urządzenie logiczne składa się z grupy programowalnych bloków FB (bloków funkcyjnych). Wejścia i wyjścia tych bloków funkcjonalnych są połączone ze sobą przez GIM (globalna macierz połączeń). Ta macierz połączeń jest rekonfigurowalna, dzięki czemu możemy modyfikować kontakty między blokami funkcjonalnymi. Będzie kilka bloków wejściowych i wyjściowych, które pozwolą nam połączyć CPLD ze światem zewnętrznym. Architekturę CPLD przedstawiono poniżej.

Ogólnie programowalny FB wygląda jak tablica bramek logicznych , gdzie można zaprogramować tablicę bramek AND, a bramki OR są stabilne. Ale każdy producent ma swój sposób myślenia, aby zaprojektować blok funkcjonalny. Wyszczególnione o / p można znaleźć, sterując sygnałami sprzężenia zwrotnego uzyskanymi z wyjść bramki OR.

Architektura CPLD

W programowaniu CPLD projekt jest najpierw kodowany w języku Verilog lub VHDL, gdy kod jest symulowany i syntetyzowany. Podczas syntezy model CPLD (urządzenie docelowe) jest wybierany ręcznie i tworzona jest lista sieci mapowania oparta na technologii. Ta lista może być zamknięta -dopasowanie do oryginalnej architektury CPLD z wykorzystaniem procesu lokalizacji i trasy, zwykle realizowanego przez oprogramowanie do lokalizacji i trasy należące do firmy CPLD. Następnie operator wykona pewne procesy potwierdzające. Jeśli wszystko jest w porządku, wykorzysta CPLD, w przeciwnym razie on to przestawi.

Problemy architektury CPLD

Rozważając złożone programowalne urządzenie logiczne do wykorzystania w projektowaniu, można wziąć pod uwagę następujące kwestie dotyczące architektury

- Technologia programowania

- Możliwości bloków funkcyjnych

- Możliwości I / O

Niektóre rodziny CPLD od różnych sprzedawców obejmują

- Rodziny Altera MAX 7000 i MAX 9000

- Rodziny Atmel ATF i ATV

- Rodzina Lattice isp LSI

- Rodzina krat (Vantis) MACH

- Rodzina Xilinx XC9500

Rodziny CPLD

Zastosowania CPLD

Zastosowania CPLD obejmują następujące elementy

- Złożone programowalne urządzenia logiczne są idealne do wysokowydajnych, krytycznych aplikacji sterujących.

- CPLD może być używany w projektach cyfrowych do wykonywania funkcji programu ładującego

- CPLD służy do ładowania danych konfiguracyjnych tablicy programowalnej przez użytkownika z pamięci nieulotnej.

- Zwykle są one używane w małych aplikacjach projektowych, takich jak dekodowanie adresów

- CPLD są często używane w wielu zastosowaniach, takich jak wrażliwe na koszty, przenośne urządzenia zasilane bateryjnie ze względu na ich mały rozmiar i zużycie małej mocy.

W związku z tym chodzi o złożoną architekturę programowalnego urządzenia logicznego i jego aplikacje. Mamy nadzieję, że lepiej zrozumieliście tę koncepcję. Ponadto wszelkie pytania dotyczące tej koncepcji lub do realizacji wszelkich projektów elektrycznych i elektronicznych , podaj cenne sugestie, komentując w sekcji komentarzy poniżej. Oto pytanie do Ciebie, jaka jest różnica między CPLD a FPGA?

Kredyty fotograficzne:

- CPLD wikimedia

- Architektura CPLD slidesharecdn